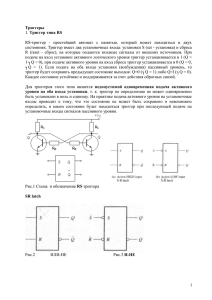

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «ВОРОНЕЖСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ» УСТРОЙСТВА ЦИФРОВОЙ ЭЛЕКТРОНИКИ Учебно-методическое пособие Составитель В.И. Парфенов Воронеж Издательский дом ВГУ 2017 Утверждено научно-методическим советом физического факультета 22 декабря 2016 г., протокол № 10 Рецензент – канд. техн. наук, доцент кафедры радиотехники и электроники ВИ МВД России И.В. Лазарев Учебно-методическое пособие подготовлено на кафедре радиофизики физического факультета Воронежского государственного университета. Рекомендуется для студентов-бакалавров 4-го курса очной формы обучения физического факультета. Для направления 03.03.03 – Радиофизика 2 1. ЦИФРОВАЯ ЛОГИКА В цифровой технике информация (кодовые слова) представляется импульсными сигналами прямоугольной формы, имеющими два фиксированных уровня напряжения. Сигналу «1» (единице) соответствует уровень «высокого» напряжения – потенциал напряжения питания, а сигналу «0» (нулю) – уровень «нулевого» напряжения, т.е. потенциал, близкий к потенциалу корпуса (общей шины). Это относится к устройствам с так называемой положительной логикой. При противоположном способе представления (негативная логика) уровни меняются местами, т.е. низкий уровень напряжения соответствует логической «1», а высокий – логическому «0». Преобразование информации в цифровых устройствах осуществляется логическими и запоминающими устройствами. Логические элементы выполняют одну или несколько простейших логических операций. Запоминающий элемент обладает способностью сохранять свое состояние при отсутствии сигнала на входе. Различают два типа цифровых устройств: комбинационные и последовательные. Комбинационные устройства – это устройства, в которых значения выходных сигналов определяются заданными в данный момент времени сочетанием входных воздействий (другими словами, отсутствуют запоминающие элементы). Последовательными устройствами называют устройства, в которых выходные сигналы зависят не только от входных воздействий в заданный момент времени, но и от их предыдущих значений (следовательно, содержат запоминающие элементы). Логические операции Для математического описания и анализа работы цифровых устройств применяется алгебра логики (булева алгебра). Под высказыванием понимается всякое предложение, в котором содержится смысл утверждения (истинности) или отрицания (ложности). Если высказывание A – истинно, то это можно обозначить A=1. Если высказывание B – ложно, то его можно записать как B=0. В основе алгебры логики Буля лежат три основных элементарных операции: ИЛИ (логическое сложение, или дизъюнкция), И (логическое умножение, или конъюнкция), НЕ (логическое отрицание, или инверсия). Обозначим логическую величину, которая может принимать значение либо «0» либо «1», через X. Тогда аксиомы алгебры логики примут вид 1) 1+X=1; 2) 0.X=0; 3) 0+X=X; 4) 1.X=X; 5) X+X=X; 3 6) X.X=X; 7) X+ X =1; 8) X. X =0; 9) X =X. Кроме этого, существуют также законы алгебры логики: 1) X1 X 2 X 2 X1 ; 2) X1 X 2 X 2 X1 ; 3) X1 X 2 X 3 4) X1 X 2 X 3 X1 ( X 2 X 3 ) ; 5) X1 ( X 2 6) X1 ( X 2 X 3 ) ( X1 8) X 1 X 2 X1 9) X1 ( X1 X 2 ) X 2 ) ( X1 X1 ( X 2 X 3) ; X 3 ) ( X1 X 2 ) ( X1 X 3 ) ; X 3 ) ; 7) X 1 X2 X1 X 2 ; X2 ; X 1 ; 10) X1 ( X1 X2) X1 . ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ Логический элемент ИЛИ имеет 2 или более входов X1, X 2 ... и один выход Y. Эта операция представляется обычно в виде: Y X1 X 2 (при наличии двух входов). То же самое действие можно записать при помощи таблицы истинности (см. Таб.1.1). Таб.1.1 X1 0 0 1 1 X2 0 1 0 1 Y 0 1 1 1 Условно-графическое изображение логического элемента, выполняющего данную функцию, приведено на рис.1.1 (как принято в отечественной и зарубежной литературах). 1 Рис.1.1. Наиболее просто операцию ИЛИ можно реализовать с помощью контактной цепи с двумя параллельно включенными ключами (см. рис.1.2). X1 Y X2 Рис.1.2 4 Сигнал Y на выходе такой цепи появится только в том случае, если хотя бы один из ключей замкнут. В цифровой электронике операцию логического сложения легко реализовать с помощью двух диодов (с независимыми входами), работающими на одно нагрузочное сопротивление R (см. рис.1.3). VD1 X1 X2 VD2 R Y Рис.1.3 Логический элемент И также содержит два или более входов X1, X 2 ... и один выход Y. Эта операция представляется обычно в виде: Y X1 X 2 (при наличии двух входов). То же самое действие можно записать при помощи таблицы истинности (см. Таб.1.2). Таб.1.2 X1 0 0 1 1 X2 0 1 0 1 Y 0 0 0 1 Условно-графическое изображение логического элемента, выполняющего данную функцию, приведено на рис.1.4 (как принято в отечественной и зарубежной литературах). & Рис.1.4. Наиболее просто операцию И можно реализовать с помощью контактной цепи с двумя последовательно включенными ключами (см. рис.1.5). 5 Y X1 X2 Рис.1.5. В цифровой электронике операцию логического умножения легко реализовать с помощью двух диодов (с независимыми входами), работающими на одно нагрузочное сопротивление RH (см. рис.1.6). +E VD1 X1 X2 VD2 R1 RH Y Рис.1.6. Логический элемент НЕ (инвертор) содержит по одному входу и выходу. Эта операция представляется обычно в виде: Y ности для данного элемента выглядит как X . Таблица истинТаб.1.3 X 0 1 Y 1 0 Условно-графическое изображение логического элемента, выполняющего данную функцию, приведено на рис.1.7 (как принято в отечественной и зарубежной литературах). 1 Рис.1.7. Контактная схема (см. рис.1.8), в отличие от ранее рассмотренных, реализуется с помощью нормально замкнутого контакта. 6 X Y Рис.1.8. Операцию инверсии обычно выполняют электронные ключи (рис. 1.9). RK +EK RB Y X Рис.1.9. Логический элемент ИЛИ-НЕ (функция Пирса): Y X1 X 2 . Таблица истинности для этого элемента приведена ниже (см. Таб.1.4). Таб.1.4. X1 0 0 1 1 X2 0 1 0 1 Y 1 0 0 0 Условно-графическое изображение логического элемента, выполняющего данную функцию, приведено на рис.1.10 (как принято в отечественной и зарубежной литературах). 1 Рис.1.10. На рис.1.11 приведена контактная схема с двумя нормально замкнутыми последовательно расположенными ключами, позволяющая реализовать такой элемент. X1 X2 Y Рис.1.11. Логический элемент И-НЕ (функция Шеффера): Y X 1 X 2 . Таблица истинности для этого элемента приведена ниже (см. Таб.1.5). 7 Таб.1.5. X1 0 0 1 1 X2 0 1 0 1 Y 1 1 1 0 Условно-графическое изображение логического элемента, выполняющего данную функцию, приведено на рис.1.12 (как принято в отечественной и зарубежной литературах). & Рис.1.12. На рис.1.13 приведена контактная схема с двумя нормально замкнутыми параллельно расположенными ключами, позволяющая реализовать такой элемент. Y X1 X2 Рис.1.13. Логический элемент Исключающее ИЛИ (сложение по модулю 2): Y X1 X 2 . Таблица истинности для этого элемента приведена в Таб.1.6, а его условное графическое изображение – на рис. 1.14. Таб.1.6. X1 X2 Y 0 0 0 0 1 1 1 0 1 =1 Рис.1.14. 8 1 1 0 ЗАДАНИЯ 1. Используя таблицы истинности, определить, какую функцию выполняет данное устройтво (проверить это экспериментально с использованием пакета MicroCap): а) б) в) г) д) 9 е) 2. Как построить а) элемент НЕ из вентилей ИЛИ-НЕ; б) элемент ИЛИ из вентилей ИЛИ-НЕ; в) элемент ИЛИ из вентилей И-НЕ. 3. Реализовать элемент Исключающее ИЛИ, используя вентили (проверить экспериментально с использованием пакета MicroCap): а) И, ИЛИ, И-НЕ; б) И, ИЛИ, НЕ. 4. Доказать законы 6-10 алгебры логики. 5. Упростить следующее выражение: X1 X 2 X 3 X1 X 2 X 3 X1 X 2 X 3 X1 X 2 X 3 . 6. Изобразить схему, реализующую логическое выражение X 1 X2X3 , используя элементы: а) ИЛИ-НЕ; б) И-НЕ. 7. Используя законы булевой алгебры, доказать следующие соотношения: а) A+B = A(B+C)+B(A+C) ; б) (AB+AB)C = (AC+BC)(AB) ; в) AB+AB +ABC = ABC+AB+BC ; г) ABC+BCD+ACD = A+D ; д) AB(AC+B)+(A+B)(ABC+ABC) =ABC+ABC . 8. Синтезируйте логическую схему, реализующую следующую функцию, используя логические элементы И-НЕ, ИЛИ-НЕ: а) Y = X1X 2 +X 2 +X1 X 2 ; б) Y = (X 2 +X1 +X 2 )X 2 ; в) Y = X 2 +(X 2 X1 )+X1 X 2 ; г) Y = X1 (X 2 +X1 )+(X 2 +X1 ) . 10 ШИФРАТОРЫ, ДЕШИФРАТОРЫ, ПРЕОБРАЗОВАТЕЛИ КОДОВ Шифратор – комбинационное логическое устройство, преобразующее десятичные числа в двоичную систему счисления. Обозначим через m число входов, последовательно пронумерованных десятичными числами (0,1,2…m-1), а через n – число выходов. Поступление сигнала на один из входов вызывает появление на выходах n-разрядного двоичного числа, соответствующего номеру возбужденного входа. Если m=2n, то такой шифратор называется полным, т.к. в нем используются все возможные комбинации сигналов на выходе. Шифрование широко применяется в различных устройствах ввода информации в цифровые системы. Такие устройства часто снабжают клавиатурой, каждая клавиша которой связана с определенным входом шифратора, а на его выходах воспроизводится двоичное число, соответствующее написанному на клавише символу. Работает шифратор в соответствии с таблицей истинности, в которой каждому десятичному числу на входе ставятся в соответствие разряды двоичного числа на выходе. Обычно обозначается шифратор как CD (от слова coder). Реализуется шифратор достаточно просто с использованием обычных логических элементов (например, элементов ИЛИ). Произносится обозначение шифратора n m как из n в m. Условно-графическое изображение шифратора (кодера) приведено на рис. 2.1. 2. 0 1 2 3 4 5 6 7 8 9 CD 1 2 4 8 Рис.2.1. Дешифратор (декодер) предназначен для обратного преобразования двоичных чисел в небольшие по значению десятичные числа. Входы дешифратора служат для подачи двоичных чисел, а выходы последовательно нумеруются десятичными числами. Дешифраторы широко используются в 11 устройствах визуальной индикации. В таких устройствах применяются семисегментные индикаторы, использующие индикаторы на жидких кристаллах и светодиоды. Поведение дешифратора описывается таблицей истинности, аналогичной таблице истинности шифратора, только в ней входные и выходные сигналы меняются местами. Обычно обозначается дешифратор как DC (от слова decoder). Реализация дешифратора также затруднений не вызывает – его можно реализовать на любых логических элементах, например, элементах НЕ и И. Условно-графическое изображение дешифратора (декодера) приведено на рис. 2.2. 1 DC 2 4 8 0 1 2 3 4 5 6 7 8 9 Рис.2.2. Преобразователями кодов, в общем случае, называют устройства, предназначенные для преобразования одного кода в другой. Преобразователи кодов обозначаются через X/Y. Преобразователи кодов часто создают по схеме дешифратор-шифратор. Дешифратор преобразует входной код в некоторое десятичное число, а затем шифратор формирует выходной код. Например, в компьютерах часто используются преобразователи Nразрядного двоичного числа в M-разрядное десятичное число и т.п. ЗАДАНИЯ. 1. Построить кодер 8×3, используя микросхему серии 74148 (Component → Digital Library → 74××120- → 148-). Составить таблицу истинности данного шифратора (кодера). 2. На инвертирующие входы I7 и EI подать сигнал единичного уровня. Определить, что при этом будет на выходах схемы A0, A1, A2. Определить, что будет на выходе A0, если на инвертирующие входы I1 и EI 12 подать логическую «единицу», а на инвертирующие входы I2, I4, I6 – логический «ноль». 3. Используя микросхему серии 74145, построить дешифратор 4×10, подавая на входы A, B, C, D сигналы, изображенные на рис.2.3. Рис.2.3. Определить таблицу истинности для данного декодера, найдя сигналы на его выходах (не забывайте, что они инвертирующие). 4. Определить, что получится на выходе, если на входы подать A=1, B=0, C=0, D=1; или A=0, B=1, C=1, D=0. Для проверки представьте эти значения как двоичные числа, переведите их в десятичные числа и сравните их с экспериментом. 5. Собрать схему, изображенную на рис.2.4. Рис.2.4. На этой схеме изображен семисегментный индикатор (Seven Segment), подключенный через дешифратор к источнику U2. Этот источник вырабатывает 4 сигнала, изображенных на рис. 2.5. 13 Рис.2.5. Декодер 4×7 построен на основе микросхемы серии 7448. Кроме того для удобства зрительного восприятия в схеме используется жидкокристаллический диод (LED) U5. Убедиться, что в процессе работы на индикаторе последовательно появляются десятичные числа от 0 до 9. Составить таблицу истинности для данного устройства, т.е. определить, что необходимо подавать на входы A, B, C, D, для того чтобы на индикаторе загорелась цифра 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. 6. Реализовать дешифратор 2×4 с таблицей истинности Таб.2.1, используя логические элементы ИЛИ, ИЛИ-НЕ. Таб.2.1. X1 X2 Y0 Y1 Y2 Y3 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1 Показать, как, используя такой дешифратор, можно реализовать логический элемент Исключающее ИЛИ, учитывая, что его работу можно описать формулой вида F =X 1 X 2 X 1 X 2 (Здесь через F обозначен выход данного эле- мента). Учесть, что в исходном состоянии на всех четырех выходах дешифратора – нули. 7. Используя встроенные в Microcap декодеры 2×4, создать декодер (дешифратор) 3×8, используя имеющиеся у них входы разрешения, позволяющие осуществлять наращивание разрядности дешифраторов. 14 3. МУЛЬТИПЛЕКСОРЫ, ДЕМУЛЬТИПЛЕКСОРЫ Мультиплексор – комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Для этих устройств принято обозначение MUX или MS. Мультиплексор содержит информационные входы, адресные входы и, как правило, разрешающие входы. Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если число информационных входов n, а число адресных входов m, причем n=2m, то такой мультиплексор называется полным. Разрешающие входы используются для расширения функциональных возможностей мультиплексора. Например, они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов и пр. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, т.е. могут блокировать работу всего устройства. Условно-графическое изображение мультиплексора приведено на рис. 3.1. X1 MUX X2 Y A Рис.3.1. Рассмотрим функционирование мультиплексора MUX 2→1 (произносится как «из двух в один»). Контактная схема подобного мультиплексора приведена на рис.3.2. Таб.3.1 содержит таблицу истинности для такого мультиплексора. A X1 Y X2 Рис.3.2 15 Таб.3.1 Адресный вход A Выход Y 0 X1 1 X2 Несложно показать, что работа подобного мультиплексора описывается формулой Y X 1 A X 2 A . Поэтому реализация подобного устройства воз- можна с использованием обычных логических элементов типа НЕ, И, ИЛИ. Если необходимо увеличить число входов, то используют каскадное включение мультиплексоров. Демультиплексор – устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор (обозначается как DMX или DMS) в функциональном отношении противоположен мультиплексору. Условно-графическое изображение демультиплексора приведено на рис. 3.3. DMX X X Y1 Y2 A Рис.3.3. Например, демультиплексор 1→2 («из одного в два») описываемый формулами Y1 X A, Y2 X A , может быть представлен в виде контактной схемы, изображенной на рис. 3.4, с таблицей истинности – Таб.3.2. A Y1 X Y2 Рис.3.4 16 Таб.3.2 Адресный вход A 0 1 Y1 X 0 Y2 0 X Для наращивания числа выходов демультиплексора используют их каскадное включение. ЗАДАНИЯ. 1. Реализовать в MicroCap схему мультиплексора 2→1 с таблицей истинности – Таб.3.1 (см. Рис. 3.5). Рис.3.5. Сигналы источников приведены ниже на рис.3.6. Рис.3.6. Определить, какой вид будет иметь сигнал на выходе данного мультиплексора. 2. Реализовать мультиплексор 4→1 с таблицей истинности Таб.3.3 и формулой вида Y A0 0 0 1 1 D0 A0 A1 D1 A0 A1 D2 A0 A1 D3 A0 A1 . Таб.3.3 A1 Y 0 D0 1 D1 0 D2 1 D3 17 В качестве входных информационных сигналов D0, D1, D2, D3 выбрать сигналы, приведенные на рис. 3.7. Рис.3.7. 3. Реализовать в MicroCap схему демультиплексора 1→2 с таблицей истинности Таб. 3.2 (см. рис.3.8). Рис.3.8. Здесь сигналы, подаваемые на информационный и адресный входы, выглядят следующим образом: Рис.3.9. Определить, как будут выглядеть сигналы на выходах данного демультиплексора. 4. Реализовать демультиплексор 1→4 с таблицей истинности Таб.3.4, выходы которого Y0, Y1, Y2, Y3 описываются формулами вида: Y 0 D A0 A1;Y1 D A0 A1;Y 2 D A0 A1;Y 3 D A0 A1 . A0 0 0 A1 0 1 Y0 D 0 Y1 0 D 18 Y2 0 0 Таб. 3.4. Y3 0 0 1 0 0 0 D 0 1 1 0 0 0 D Структуры информационного D и двух адресных A0 и A1 сигналов приведены на рис. 3.10. Рис.3.10. Определить выходные сигналы Y0–Y3 демультиплексора. 5. Показать, каким образом мультиплексор 4→1 с таблицей истинности Таб.3.3 может быть использован для построения логического устройства, выполняющего функцию F =X 1 X 2 X 3 . Учесть, что в этом слу- чае сигналы X1 и X2 следует подавать на адресные входы A1 и A2. 6. Определите таблицу истинности мультиплексора 8→1 с тремя адресными входами, выход которого описывается выражением Y A2 A1 A0 X 0 A2 A1 A0 X 1 A2 A1 A0 X 2 A2 A1 A0 X 3 . A2 A1 A0 X 4 A2 A1 A0 X 5 A2 A1 A0 X 6 A2 A1 A0 X 7 4. СУММАТОРЫ, КОМПАРАТОРЫ Сумматор – комбинационное устройство, предназначенное для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел A и B. Обозначим S – результат суммирования, P – значение переноса в старший разряд. Тогда таблицу истинности такого устройства можно представить в виде Таб.4.1. Таб.4.1. A B P S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 Несложно заметить, что для результата сложения справедливы следующие формулы: S A B A B A B, P A B . Устройство, реализующее таблицу истинности Таб.4.1, называется полусумматором (HS). Так как полусумматор имеет только два входа, он может использоваться для 19 суммирования лишь в младшем разряде. Условно-графическое изображение полусумматора приведено на рис. 4.1. A HS B S P Рис.4.1. При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Это будет полный одноразрядный сумматор (SM). Условно-графическое изображение сумматора приведено на рис. 4.2. Таблица истинности такого сумматора представлена в Таб.4.2. Pi-1 SM M S Si P Pi Ai Bi Рис.4.2 Ai 1 1 0 0 1 1 0 0 Bi 1 0 1 0 1 0 1 0 Pi-1 1 1 1 1 0 0 0 0 20 Si 1 0 0 1 0 1 1 0 Таб.4.2. Pi 1 1 1 0 1 0 0 0 Четырехразрядный сумматор позволяет складывать уже два четырехразрядных двоичных числа. Его можно построить из четырех последовательно соединенных одноразрядных сумматоров. Цифровые компараторы выполняют сравнение двух чисел, записанных в двоичном коде. Они могут определять, какое соотношение имеет место между двумя числами A и B: A=B или A>B или A<B. Цифровые компараторы имеют три выхода. Схема компаратора в пакете MicroCap выглядит следующим образом (рис. 4.3). Рис.4.3. Здесь U4 (B) и U6 (A) источники сравниваемых сигналов, сигнал на выходе 4 описывается формулой D AB (появление сигнала на этом выходе озна- чает, что A<B); сигнал на выходе 6 описывается формулой C AB (появление сигнала на этом выходе означает, что A>B); наконец, сигнал на выходе 7 описывается формулой F AB AB (появление сигнала на этом выходе означает, что A=B). Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа. Применяя компаратор для каждого разряда, например, четырехзначных чисел, и определяя значения F1, F2, F3, F4 логических переменных на выходах компараторов, факт равенства A=B установим, когда F F1 F2 F3 F4 1. Если же F=0, то A B . Неравенство A>B выполняется в следующих четырех случаях: или ( A4 B4 A3 B3 ) или ( A4 B4 A3 B3 A2 A4 B2 ) B4 или или ( A4 B4 A3 B3 A2 B2 A1 B1 ) . Здесь A4, B4 – старшие разряды чисел A и B. Если поменять местами Ai и Bi , то будет выполняться неравенство A<B. 21 ЗАДАНИЯ. 1. Собрать в MicroCap схему полусумматора, как это показано на рис.4.4. В качестве источников входных сигналов использовать сигналы, изображенные на рис. 4.5. Рис.4.4. Рис.4.5. Убедиться в корректной работе такого устройства, удовлетворяющей таблице истинности Таб. 4.1. 2. Из двух полусумматоров создать одноразрядный сумматор в соответствии со схемой, изображенной на рис.4.6 (в MicroCap создать с помощью Macros полусумматор). Pi-1 Ai Bi HSH S S P HSH S S P P Рис.4.6. P 22 Si 1 Pi Проверить, удовлетворяет ли его работа таблице истинности Таб. 4.2. 3. Собрать схему компаратора, изображенную на рис. 4.3. В качестве источников входных сигналов использовать сигналы, представленные на рис. 4.7. Рис.4.7 Проанализировать поведение выходов компаратора 4, 6 и 7 в зависимости от соотношения между входными сигналами. Показать, что ненулевые сигналы на этих выходах появляются только при определенных соотношениях между входными сигналами. 4. Показать, что для одноразрядного сумматора его выходные сигналы описываются выражениями: Pi Ai Bi Bi Pi 1 Pi 1 Ai , Si Ai Pi Bi Pi Pi 1 Pi Ai Bi Pi 1. 5. Реализовать двухразрядный сравнение двух двухразрядных чисел. компаратор, осуществляющий 5. ТРИГГЕРЫ. Триггер (trigger – спусковая схема) – устройство с двумя устойчивыми состояниями, скачком переходящие из одного состояния в другое под воздействием входных сигналов. Входы триггера делятся на информационные и управляющие. Информационные входы используются для управления состоянием триггера. Управляющие входы используются для предварительной установки триггера в некоторое состояние и для синхронизации. В общем случае триггер имеет два выхода: прямой и инверсный. Триггер относится к последовательным цифровым узлам, т.к. его выходное состояние зависит не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени. На рис. 5.1 приведена классификация триггеров. 23 ТРИГГЕРЫ По способу управления RS По типу синхронизации Синхронные JK … По внутренней организации Асинхронные Одноступенчатые Двухступенчатые D Со статической синхронизацией С динамической синхронизацией Рис. 5.1. Отличительной особенностью асинхронного триггера является то, что запись информации в нем осуществляется статическим способом, т.е. непосредственно с поступлением информационного сигнала на его вход. Запись информации в синхронный триггер осуществляется только при подаче разрешающего (тактирующего) импульса. Среди синхронных триггеров различают триггеры, срабатывающие по уровню (в момент прихода тактирующего сигнала, т.е. по переднему фронту), и триггеры с внутренней задержкой, срабатывающие после окончания тактирующего сигнала (т.е. по заднему фронту). Такое управление синхронным триггером называется динамическим. Кроме того, триггеры подразделяются на одноступенчатые и двухступенчатые в зависимости от числа тактирующих сигналов, необходимых для перевода триггера из одного состояния в другое. RS-триггер Существуют асинхронные и синхронные RS-триггеры. Начнем с асинхронного RS-триггера, условно-графическое изображение которого приведено на рис. 5.2. 24 R T Q Q S Рис.5.2 Входной сигнал S устанавливает триггер в положение Q=1 (S – происходит от английского слова SET – установка, R – от английского RESET – сброс – переключает триггер в положение Q=0). Работу триггерных схем можно описать с помощью таблиц, аналогичных таблицам истинности. Но в данном случае они иллюстрируют переход значений выходного сигнала от Qn к Qn+1 и ее называют таблицей переключения. Здесь индекс n характеризует рассматриваемый момент времени. Таблица переключений асинхронного RS-тригера приведена ниже (см. Таб.5.1). Алгебраическое уравнение, описывающее работу триггера, может быть представлено в виде: Qn 1 R( S Qn 1 ) . Sn Rn Qn Qn+1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 X X Таб.5.1 Режим работы Режим хранения Режим записи «0» Режим установки «1» Запрещенная комбинация Если S=1, R=0, то триггер переходит в единичное состояние, если же S=0, R=1, то – в нулевое состояние. Комбинация S=1, R=1 является запрещенной, т.к. при этом триггер под воздействием внутренних факторов может равновероятно перейти как в единичное, так и в нулевое состояние. Если 25 S=0, R=0, то триггер сохраняет предыдущее состояние (подобная комбинация называется памятью). RS-триггер легко может быть построен на основе простейших логических элементов типа ИЛИ-НЕ или И-НЕ. Если он выполнен на базовых элементах ИЛИ-НЕ и переключается единичными входными сигналами (как это описано выше), то он называется триггером с прямыми входами. Если же он выполнен на элементах И-НЕ, то он называется триггером с инверсными входами. Рассмотренный RS-триггер при наличии помех работает ненадежно, т.к. короткие импульсы, попадающие на R или на S входы, могут изменить состояние триггера. Для повышения устойчивости используют синхронный RS-триггер, состояние которого может измениться только, если на входе С будет логическая единица. Итак, синхронный RS-триггер (или RST-триггер) имеет дополнительный С-вход, на который подают импульсы синхронизации (см. рис.5.3). T S Q С Q R Рис.5.3. При отсутствии сигнала на С-входе (С=0) входы R и S оказываются отключенными от собственно триггера и изменение состояний на этих входах не может изменить состояние триггера. Таблица переключений синхронного RS-триггера приведена ниже в Таб.5.2. Алгебраическое уравнение, описывающее работу синхронного RS-триггера, может быть представлено в виде: Qn CS CRQn . 1 С Sn Rn Qn Qn+1 0 0 1 * * 0 * * 0 0 1 0 0 1 0 26 Таб.5.2. Режим работы Режим хранения Режим хра- 1 0 0 1 1 нения 1 0 1 0 0 Режим записи «0» 1 0 1 1 0 1 1 0 0 1 Режим установки «1» 1 1 0 1 1 1 1 1 0 X Запрещенная комбинация 1 1 1 1 X В этой таблице «*» означает любое значение. Нетрудно заметить, что при С=1 таблицы Таб.5.2 и Таб.5.1 совпадают. D-триггер D-триггер (Delay – задержка) имеет два входа – информационный D и тактовый С. Запись информации в нем производится только в моменты поступления тактовых импульсов на вход С (С=1). В этом случае выходной сигнал Q повторяет входной D. Условное графическое изображение Dтриггера приведено на рис. 5.4. D T Q Q C Рис.5.4. Если в RS-триггере для записи логического «0» и логической «1» требуются разные входы, то в D-триггере информационный вход всего один. Кроме того, если в RS-триггере имеются запрещенные комбинации, то в Dтриггере они отсутствуют. Таблица переключений синхронного D-триггера приведена далее в Таб.5.3. Уравнение, описывающее работу D-триггера имеет вид: Qn 1 DnCn Qn (C n D) . С Dn Qn Qn+1 0 * 0 0 27 Таб.5.3. Режим работы Режим хра- 0 1 1 * 0 1 1 * * 1 0 1 нения Режим записи информации Информация записывается в триггер при поступлении тактирующего импульса, а на выходе появляется в момент окончания тактирующего импульса. Эта информация может быть использована, когда придет следующий тактирующий импульс, т.е. в следующем такте. Это и объясняет название данного триггера – триггер задержки (на один такт). Динамический D-триггер В динамических (работающих по фронту) D-триггерах сигнал запоминается только в момент изменения сигнала на входе С с единичного потенциала на нулевой (или наоборот). Преимущество динамического триггера перед триггером со статическим управлением заключается в том, что динамический триггер реагирует на информационные сигналы только в моменты изменения тактовых импульсов. Это исключает возможность неправильного срабатывания триггера со статическим управлением, возможное тогда, когда информационный сигнал изменяет свое значение непосредственно перед переходом от единицы к нулю при С=1. Условно графическое изображение D-триггера, запоминающего информацию по заднему (спадающему) фронту тактового сигнала, приведено на рис.5.5. D TT Q Q C Рис.5.5. Если черта на входе С будет иметь противоположный наклон, то это будет D-триггер, работающий по переднему (нарастающему) фронту сигнала. В D-триггере сигнал на входе по сигналу синхронизации записывается и передается на выход. Так как информация на выходе остается неизменной до прихода очередного импульса синхронизации, то D-триггер называют также триггером-защелкой или триггером с запоминанием информации. 28 Т-триггер Т-триггер (T – Trumbler – опрокидыватель) имеет только один вход – информационный вход Т. Его переключение происходит в момент поступления очередного входного импульса. Его еще называют счетным триггером. Счетным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. При поступлении первого импульса состояние триггера становится единичным, а с приходом второго импульса Т-триггер снова сбрасывается в исходное (нулевое) состояние. Условно графическое изображение такого триггера приведено на рис. 5.6. TT Q Т Q Рис.5.6. Уравнение, описывающее работу Т-триггера, имеет вид: Qn 1 TQn T Q n . Т-триггеры используются при построении схем различных счетчиков и делителей частоты. JK-триггеры В JK-триггере устранена неопределенность, возникающая в RSтриггере при S=R=1. А в остальном он полностью подобен синхронному RS-триггеру. Его условно графическое изображение показано на рис.5.7, а таблица переключений в Таб.5.4 (J происходит от английского слова Jump, а K – от английского слова Keep). 29 TT J Q С Q K Рис.5.7. С Jn 0 0 1 1 1 1 1 1 1 1 Уравнение, Qn 1 J n Qn Kn Qn Qn+1 * * * * 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 описывающее 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0 JK-триггера, работу Таб.5.4 Режим работы Режим хранения Режим хранения Режим записи «0» Режим установки «1» Счетный режим имеет вид: K nQn . JK-триггеры, в силу своей универсальности, могут вы- полнять функции других триггеров. Отметим также, что зачастую все триггеры могут иметь дополнительные входы: предустановки (PRE) и очистки (CLR). Они позволяют устанавливать триггер в нужное начальное состояние. Триггер устанавливается в единичное состояние подачей логической «1» в виде импульсного сигнала на вход предустановки и остается в этом состоянии после снятия импульса предустановки. Аналогично триггер устанавливается в состояние логического «0» временной подачей логической «1» на вход очистки. ЗАДАНИЯ. 1. Показать, что синхронный RS-триггер может быть реализован на элементах И-НЕ так, как это показано ниже на рис. 5.8. С этой целью в 30 программе MicroCap собрать данную схему и сравнить ее работу с работой встроенного RS-триггера (Component → Digital Primitives → Gated FlipFlops/Latches → SRFF). Определить для этого триггера таблицу переключений, сравнив ее с Таб.5.2. S & & Q C & & Q R Рис.5.8. 2. Показать, что D-триггер может быть реализован на элементах И-НЕ так, как это показано ниже на рис. 5.9. С этой целью в программе MicroCap собрать данную схему и сравнить ее работу с работой встроенного D-триггера (Component → Digital Primitives → Gated Flip-Flops/Latches → Latch). Определить для этого триггера таблицу переключений, сравнив ее с Таб.5.3. D & & Q & & Q C Рис.5.9. 31 3. Сравнить работу следующих, встроенных в Microcap, триггеров: синхронного RS-триггера (Component → Digital Primitives → Gated FlipFlops/Latches → SRFF), D-триггера (Component → Digital Primitives → Gated Flip-Flops/Latches → Latch), динамического D-триггера (Component → Digital Primitives → Edge-Triggered Flip-Flops → DFF), JK-триггера (Component → Digital Primitives → Edge-Triggered Flip-Flops → JKFF). С этой целью подать на их входы следующие сигналы, изображенные на рис. 5.10. Рис.5.10. На этом рисунке первый сигнал подается на R, D и J-входы соответствующих триггеров, второй – на S и K входы соответствующих триггеров, и, наконец, третий – на С-входы всех триггеров. 4. Собрать в MicroCap схему, изображенную на рис.5.11. Рис.5.11. Здесь источники U4, U6 создают сигналы, представленные на рис.5.12. Рис.5.12. 32 Убедиться, что сигналы на выходах 11, 8 и 19 совпадают. Определить, какой триггер здесь реализован различными способами. Показать, что необходимо изменить в данной схеме, чтобы все три устройства срабатывали не по заднему, а по переднему фронту сигнала, подаваемого на тактовые входы. 5. Собрать в MicroCap схему, изображенную на рис.5.13. Рис.5.13. Здесь источник U6 создает сигнал, представленный на рис.5.14. Рис.5.14. Убедиться, что сигналы на выходах 5, 15 и 20 совпадают. Определить, какой триггер здесь реализован различными способами. 6. Определить уровни сигналов на входах асинхронного RSтриггера с прямыми входами (построенных на элементах ИЛИ-НЕ), при которых триггер последовательно переходит в состояния: Q=0,1,1,0,0,1,0,0,1,1. 6. СЧЕТЧИКИ ИМПУЛЬСОВ, РЕГИСТРЫ Счетчики импульсов – это последовательные цифровые устройства, обеспечивающие хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на единицу. По существу счетчик представляет собой совокупность соеди33 ненных определенным образом триггеров. Счетчики используются для построения таймеров и для выборки инструкций из ПЗУ в микропроцессорах. Кроме того, они могут использоваться как делители частоты в синтезаторах частоты. Основные характеристики счетчиков – это модуль счета, емкость и коэффициент деления частоты. Модуль счета – это число устойчивых состояний (число импульсов), которое возвращает счетчик в исходное состояn ние. Для двоичных счетчиков модуль счета определяется как 2 , где n – количество триггеров в счетчике. Емкость – это максимальное число импульсов, которое может быть сосчитано счетчиком. Для двоичных счетчиков n емкость равна 2 -1. Коэффициент деления частоты показывает соотношение между частотой импульсов на входе счетчика и частотой на выходе последнего триггера. Для двоичных счетчиков коэффициент деления равен n 2 .Счетчики обозначаются еще как CT – counter. Условно графическое обозначение счетчика приведено на рис.6.1 (для примера показан двоичный счетчик с суммирующим действием). C1 CT2 C2 1 2 4 8 R Рис.6.1 Счетчики могут быть построены как на Т-триггерах, так и на JK-триггерах. Регистр – устройство, предназначенное для хранения информации, представленной в двоичной форме. Они широко используются в компьютерной технике. Действительно, обмен информации между различными узлами вычислительной техники (например, процессор – память) осуществляется с помощью битовых комбинаций различной фиксированной длины. Такие комбинации называют машинными словами. Как правило, это многоразрядные числа, представленные в двоичной форме. Регистр обычно состоит из связанных друг с другом триггеров, каждый из которых служит для хранения «0» или «1» (одного разряда двоичного числа). Количество триггеров определяет разрядность регистра. Регистры могут выполнять также 34 операции приема, передачи и преобразования информации, обеспечиваемые системой управления. В зависимости от выполняемой функции регистры подразделяются на параллельные и сдвиговые. Для хранения n-разрядного машинного слова регистр должен содержать n триггеров. Регистры обычно строятся на основе D-триггеров (как динамических, так и статических). Пример условного графического изображения параллельного регистра приведен на рис. 6.2. Обозначение для сдвигового регистра практически такое же, за исключением того, что обозначение RG заменяется на RG . D0 RG D1 Q0 Q1 D2 Q2 D3 Q3 C Рис.6.2 Параллельные регистры обычно служат для запоминания многоразрядного машинного слова. Если разрядность регистра требуется увеличить, то регистры меньшей разрядности соединяются параллельно. Сдвиговый (последовательный) регистр обычно служит для преобразования последовательного кода в параллельный и наоборот, а также для сдвига хранимого в регистре числа на определенное количество разрядов влево или вправо. При построении сдвиговых регистров используют только D-триггеры, работающие по фронту. Преобразование последовательного кода в параллельный в сдвиговом регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход С регистра. Через n тактов число окажется принятым в регистр и может быть затем снято в параллельной форме с выходов триггеров всех разрядов. Перевод числа из параллельной формы в последовательную может быть выполнен сдвиговым регистром, у которого предусмотрены входы для приема числа в параллельной форме. После записи в регистр n-разрядного слова на выходе триггера первого разряда мы получим младший разряд числа. При сдвиге числа на один разряд вправо в 35 триггер первого разряда передается цифра второго разряда и т.д. Таким образом, при повторении сдвигов вправо n-1 раз на выходе триггера первого разряда регистра последовательно появляются цифры всех n разрядов. ЗАДАНИЯ 1. Проанализировать работу суммирующего счетчика, построенного на основе JK-триггеров, структура которого приведена на рис. 6.3. Рис.6.3. В качестве источников U13, U15 и U16 (первые два из которых используются для предустановки) использовать источники, формирующие сигналы, изображенные на рис.6.4. Рис.6.4. Несложно заметить, что на все J и K входы поданы логические «1». Определить, что получится на выходах 4, 6, 8 и 10 на определенных промежутках времени, определяемыми сигналом на С-входе. На каком из выходов появляется старший, а на каком – младший разряд подсчитанного числа импульсов? Обратите внимание на роль сигнала CLRB. Определить, что появится на инверсных выходах 5, 7, 9 и 11. 2. Проанализировать работу четырехразрядного вычитающего счетчика с последовательным переносом, структура которого изображена на рис. 6.5. 36 Рис.6.5 Источники сигналов – такие же, как и на рис.6.3. Несложно заметить, что отличие рис.6.5 от рис.6.3 заключается только в том, что JK-триггеры на последнем рисунке соединены последовательно через инверсные выходы. Получить и проанализировать сигналы на выходах 15, 17, 19 и 21. Почему такой счетчик называется вычитающим? 3. Реализовать в программе MicroCap параллельный четырехразрядный регистр, построенный на четырех D-триггерах, схема которого приведена на рис.6.6. Рис.6.6. На входы 4, 9, 14 и 19 устройства подать сигналы вида Рис.6.7. 37 Определить структуру сигналов на выходах 5, 10, 15 и 20. Сделать вывод о назначении устройства. Соединив параллельно 4 подобных регистра, получить шестнадцатиразрядный регистр. 4. Реализовать в программе MicroCap сдвиговый четырехразрядный регистр, построенный на четырех D-триггерах, схема которого приведена на рис.6.8. Рис.6.8. Заметим, что в отличие от параллельного регистра (рис.6.6), сдвиговый регистр (рис.6.8) построен на динамических D-триггерах. Источники входного сигнала и тактирующего сигнала выбрать так, как это показано ниже на рис.6.9. Несложно заметить, что на интервале времени [0;400]ns входной сигнал имеет вид 1001, причем каждый бит сопровождается тактовым импульсом синхронизации, которые поступают на входы С. Рис.6.9. Определить сигналы на выходах 32, 34, 36 и 38 в разные моменты времени. Проанализировать продвижение битов информации по выходам регистра. Определить, что будет после четырех тактов. Построить временную диаграмму работы сдвигающего регистра на Dтриггерах, в который записано число 1101. 5. Суммирующий счетчик состоит из 5 ячеек. Исходное состояние триггеров 00000. На вход поступило 155 импульсов. Какие состояния примут триггеры счетчика. 38 6. Построить вычитающий счетчик из D-триггеров, который может посчитать любое количество импульсов до 63. В какое состояние перейдут триггеры счетчика после поступления на его вход 38 импульсов. 7. Построить устройство, которое преобразует последовательность импульсов с частотой 256 КГц в последовательность с частотой 16 КГц. Контрольные задания. 1. Спроектировать устройство, зажигающее светодиод тогда и только тогда, когда 4 из 6 сигналов принимают единичные значения. 2. Реализовать с помощью мультиплексора цифровое устройство, работающее в соответствии с алгоритмом: F ABC BCD ABCD BC ABCD . 3. Спроектировать устройство, пропускающее на выход каждый седьмой импульс. 4. Реализовать с помощью мультиплексора устройство, выполняющее следующую логическую функцию: F AB AB . 5. Что будет на выходе JK-триггера, если на его С-вход подать последовательность прямоугольных видеоимпульсов. 6. Реализовать синхронный RS-триггер на логических элементах ИЛИ-НЕ. 7. Показать, каким образом D-триггер может быть реализован через синхронный RS-триггер. 8. Как будет функционировать D-триггер, если его выход Q свя- зать с входом D (объяснить, что такое «паразитная генерация»). 9. Определить уровни сигналов на входе синхронного D-триггера, при которых он последовательно переходит в состояния: Q=0,0,1,1,0,1,1,0. 10. Представить JK-триггер, используя синхронный RS-триггер и необходимые логические элементы. 11. Реализовать параллельный двухразрядный регистр на RSTтриггерах. 12. Исходное состояние суммирующего счетчика 01101. Определить его состояние, если на его вход поступило 99 импульсов. 13. Построить счетчик на JK-триггерах, чтобы он мог сосчитать любое количество импульсов от 0 до 55. 14. Исходное состояние вычитающего счетчика 10100. На его вход поступило 10 импульсов. Какое состояние примут триггеры счетчика после 39 поступления на его вход этих импульсов. Как изменится это состояние, если поступит еще 32 импульса. 15. Построить схему регистра на JK-триггерах для записи числа 11101, начиная с цифры младшего разряда. Библиографический список 1. Фомичев Ю. М. Электроника. Элементная база, аналоговые и цифровые функциональные устройства : учеб. пособие / Ю. М. Фомичев, В. М. Сергеев ; Томский политехнический университет. – Томск : Изд-во Томского политехнического университета, 2011. – 275 с. 2. Прянишников В. А. Электроника : полный курс лекций / В. А. Прянишников. – 3-е изд., испр. и доп. – СПб. : Учитель и ученик : КОРОНА принт, 2003. – 416 с. 3. Нефедов В. И. Основы радиоэлектроники и связи : учебник для вузов / В. И. Нефедов. – 2-е изд., перераб. и доп. – М. : Высш. шк., 2002. – 510 с. 4. Клочков Г. Л. Цифровые устройства и микропроцессоры : учебник / Г. Л. Клочков. – Воронеж : ВИРЭ, 2005. – 320 с. 5. Угрюмов Е. П. Цифровая схемотехника / Е. П. Угрюмов. – СПб. : БХВ – Санкт-Петербург, 2000. – 528 с. 6. Фрике К. Вводный курс цифровой электроники / К. Фрике. – М. : Техносфера, 2003. – 432 с. 7. Антонов О. Г. Цифровые устройства и микропроцессоры : учебное пособие / О. Г. Антонов, Е. Ю. Мигунова. – СПб. : СЗТУ, 2006. Часть 1 : Цифровые устройства. – 82 с. 8. Иноземцев В. А. Изучение элементной базы цифровой техники / В. А. Иноземцев. – Брянск : Изд-во БГУ, 2002. – 110 с. 40 Содержание Цифровая логика ................................................................................................. 3 Шифраторы, дешифраторы, преобразователи кодов .................................... 11 Мультиплексоры, демультиплексоры ............................................................. 15 Сумматоры, компараторы ................................................................................ 19 Триггеры............................................................................................................. 23 Счетчики импульсов, регистры ....................................................................... 33 Контрольные задания ....................................................................................... 39 Библиографический список ............................................................................. 40 41 Учебное издание УСТРОЙСТВА ЦИФРОВОЙ ЭЛЕКТРОНИКИ Учебно-методическое пособие Составитель Парфенов Владимир Иванович Издано в авторской редакции Подписано в печать 08.02.2017. Формат 60ൈ84/16 Уч.-изд. л. 1,8. Усл. печ. л. 2,4. Заказ 58 Издательский дом ВГУ 394018, г. Воронеж, пл. им. Ленина, 10 42