Логические схемы

реклама

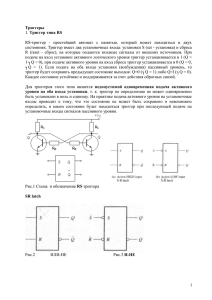

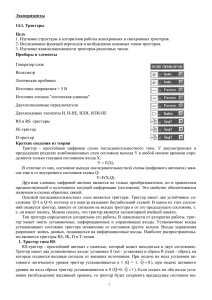

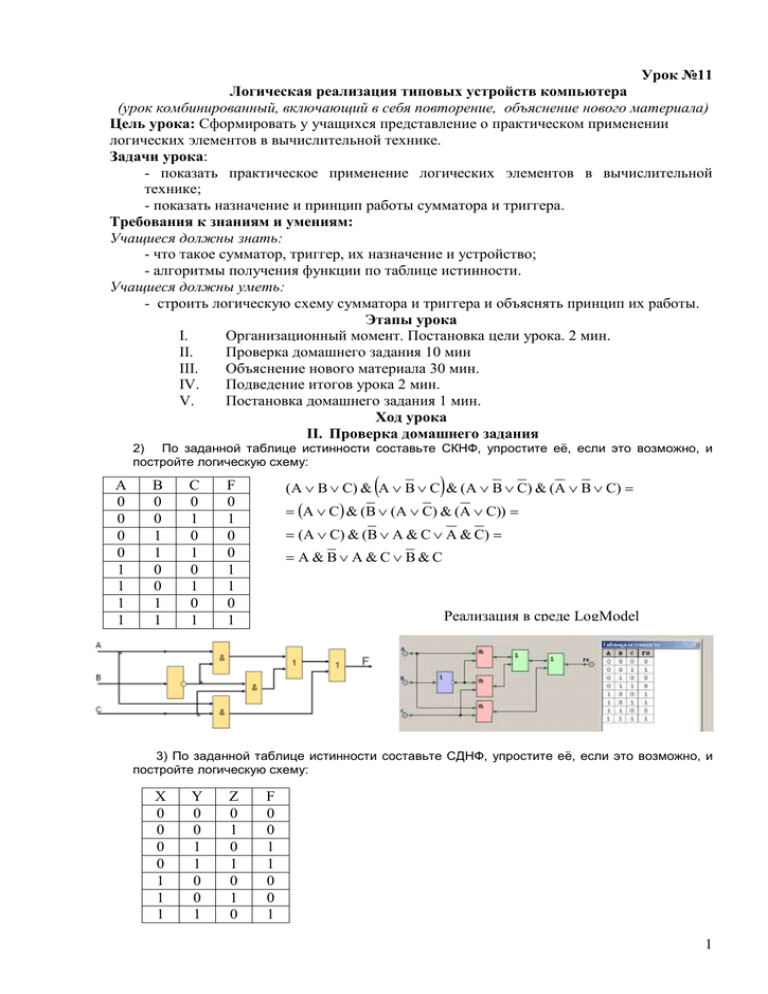

Урок №11 Логическая реализация типовых устройств компьютера (урок комбинированный, включающий в себя повторение, объяснение нового материала) Цель урока: Сформировать у учащихся представление о практическом применении логических элементов в вычислительной технике. Задачи урока: - показать практическое применение логических элементов в вычислительной технике; - показать назначение и принцип работы сумматора и триггера. Требования к знаниям и умениям: Учащиеся должны знать: - что такое сумматор, триггер, их назначение и устройство; - алгоритмы получения функции по таблице истинности. Учащиеся должны уметь: - строить логическую схему сумматора и триггера и объяснять принцип их работы. Этапы урока I. Организационный момент. Постановка цели урока. 2 мин. II. Проверка домашнего задания 10 мин III. Объяснение нового материала 30 мин. IV. Подведение итогов урока 2 мин. V. Постановка домашнего задания 1 мин. Ход урока II. Проверка домашнего задания 2) По заданной таблице истинности составьте СКНФ, упростите её, если это возможно, и постройте логическую схему: А 0 0 0 0 1 1 1 1 В 0 0 1 1 0 0 1 1 С 0 1 0 1 0 1 0 1 (A B C) & A B C & (A B C) & (A B C) F 0 1 0 0 1 1 0 1 A C & (B (A C) & (A C)) (A C) & (B A & C A & C) A&B A&C B&C Реализация в среде LogModel 3) По заданной таблице истинности составьте СДНФ, упростите её, если это возможно, и постройте логическую схему: X 0 0 0 0 1 1 1 Y 0 0 1 1 0 0 1 Z 0 1 0 1 0 1 0 F 0 0 1 1 0 0 1 1 1 1 1 0 A&B&C A&B&C A&B& A & B A & B & C B & (A B & (A C) 2 Реализация в среде LogModel 1)Задача. Три преподавателя отбирают задачи для олимпиады. Задач несколько. По каждой из задач каждый из преподавателей высказывает свое мнение: легкая задача (0) или трудная (1). Задача включается в олимпиадное задание, если не менее 2 преподавателей отметили ее как трудную, но если все три преподавателя считают ее трудной, то такая задача не включается в олимпиадное задание как слишком трудная. Требуется составить функциональную схему устройства, которое на выходе выдавало бы 1, если задача включается в олимпиадное задание, и 0, если не включается. Алгоритм решения: Составить таблицу истинности. Определить логическую функцию. Построить логическую схему. Проверить устройство в среде LogModel Задача включается в олимпиадное задание, если не менее 2 преподавателей из 3-х (А,В,С) отметили её как трудную. Обозначения:: 0 – задача нетрудная, 1 - задача трудная. X 0 0 0 0 1 1 1 1 Y 0 0 1 1 0 0 1 1 Z 0 1 0 1 0 1 0 1 F 0 0 0 1 0 1 1 0 F(A, B, C) A & B & C A & B & C A & B & C Реализация в среде LogModel III.Объяснение нового материала Обработка любой информации на компьютере сводится к выполнению процессором различных арифметических и логических операций. Для этого в состав процессора входит так называемое арифметико-логическое устройство (АЛУ). Оно состоит из ряда устройств, построенных на рассмотренных выше логических элементах. Важнейшими из таких устройств являются триггеры, полусумматоры, сумматоры, шифраторы, дешифраторы, счетчики, регистры. 3 Этапы конструирования логического устройства. Конструирование логического устройства состоит из следующих этапов: I. Построение таблицы истинности по заданным условиям работы проектируемого узла (т.е. по соответствию его входных и выходных сигналов). II. Конструирование логической функции данного узла по таблице истинности, ее преобразование (упрощение), если это возможно и необходимо. III. Составление функциональной схемы проектируемого узла по формуле логической функции. IV. Реализация полученной схемы в «металле». В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора являются сумматоры, которые как раз и обеспечивают такое сложению. Одноразрядный полусумматор Попробуем, действуя по плану, сконструировать устройство для сложения двух двоичных чисел (одноразрядный полусумматор). Пусть нам необходимо сложить двоичные числа A и B. Через P и S обозначим первую и вторую цифру суммы: A + B = PS. 1). Таблица истинности, определяющая результат сложения, имеет вид: A B P S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 2). Сконструируем функции P(A,B) и S(A,B) по этой таблице: P A & B; S A & B A & B A & B A & B (A & B A) & (A & B B)( закон дистрибутивности) (A A) & (A B) & (A B) & (B B)(законы исключённоготретьего и дистрибутивности) 1 & (A B) & (A B) & 1(закон де Моргана ) (A B) & A & B 3). Теперь можно построить функциональную схему одноразрядного полусумматора: P A&B S (A B) & A & B Данная схема реализует суммирование одноразрядных двоичных чисел без учёта переноса из младшего разряда (сумматор на два входа и два выхода) 4 Полный одноразрядный сумматор Полный одноразрядный сумматор должен иметь три входа: А, В, - слагаемые и Р0 – переос из младшего разряда и два выхода: сумму S и перенос Р. Идея построения полного сумматора точно такая же, как и полусумматора. A 0 0 1 1 0 0 1 1 B 0 1 0 1 0 1 0 1 P0 0 0 0 0 1 1 1 1 P 0 0 0 1 0 1 1 1 S 0 1 1 0 1 0 0 1 P (A & B) (A & P0 ) (B & P0 ) S (A B P0 ) & P0 (A & B & P0 ) Домашнее задание: 1) Построить СДНФ для Р и S по таблице истинности и упростить. 2)* Построить логическую схему одноразрядного сумматора в среде LogModel. Многоразрядный сумматор Процессор, как правило складывает многоразрядные двоичные числа. Для вычисления суммы многоразрядных чисел используется многоразрядный сумматор, в котором на каждый разряд ставится одноразрядный сумматор и выход – перенос сумматора младшего разряда подключается к входу сумматора старшего разряда. Общая схема сумматора: Триггер Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер. Это устройство позволяет запоминать, хранить и считывать информацию. Каждый триггер может хранить 1 бит информации. Триггер - электронная схема, применяемая для хранения значения одноразрядного двоичного кода. Термин триггер происходит от английского слова trigger - защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flipflop, что в переводе означает "хлопанье". Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить ("перебрасываться") из одного электрического состояния в другое. Воздействуя на входы триггера, его переводят в одно из двух возможных состояний (0 или 1). С поступлением сигналов на входы триггера в зависимости от его состояния либо происходит переключение, либо исходное состояние сохраняется. При отсутствии входных сигналов триггер сохраняет свое состояние сколь угодно долго. Существуют разные варианты исполнения триггеров в зависимости от элементной базы (И-НЕ, ИЛИ-НЕ) и функциональных связей между сигналами на входах и выходах (RS, JK, T, D и другие). Самый распространённый тип триггера - это RS-триггер (S и R соответственно от английских set - установка, и reset - сброс). RS-триггер можно построить из двух 5 дизъюнкторов (ИЛИ) и двух инверторов (НЕ). Триггер имеет два входа S и R (set установка, и reset - сброс) и два выхода Q(прямой) и Q (инверсный). Входы и выходы элементов соединены кольцом: первый выход соединён со вторым входом и второй выход с первым входом. В обычном состоянии на входы триггера подан сигнал 0, и триггер хранит 0. Рассмотрим по схеме прохождение сигнала при подаче на вход S(установка) сигнала 1: видим, что триггер переходит в состояние 1 и будет устойчиво находится в нём и после того, как сигнал на входе исчезнет. Триггер запомнил 1. Для того чтобы сбросить информацию и подготовиться к приёму новой, подаётся сигнал 1 на вход R(сброс), после чего триггер возвратится с исходному «нулевому» состоянию. Один триггер хранит один бит информации. Для хранения одного байта информации необходимо 8 триггеров. Современные микросхемы памяти содержат миллионы триггеров. Задача1. Построим таблицу, описывающую состояние входов и выходов RS-триггера. 1) Если на входы поступают сигналы S=0 и R=0, то триггер находится в режиме хранения, на выходах сохраняются установленные ранее значения. 2) Если на установочный вход S поступает на короткое время сигнал 1, то триггер переходит в Входы Состояние состояние 1 и после того, как сигнал на входе S станет Q S R равен 0, триггер будет сохранять это состояние, то есть 0 0 Q будет хранить 1. 1 0 1 3) При подаче 1 на вход R триггер перейдёт в состояние 0. 0 1 0 4) Подача на оба входа S и R логической единицы может 1 1 Недопусти привести к неоднозначному результату. Поэтому такая мо комбинация входных сигналов запрещена. Понятие о регистре Некоторое количество триггеров, объединенных вместе общей системой управления, называется регистром. Регистры содержатся в различных вычислительных узлах компьютера - процессоре, периферийных устройствах и т.д. Регистр - это устройство, предназначенное для хранения многоразрядного двоичного числового кода, которым можно представлять и адрес, и команду, и данные. Упрощенно регистр можно представить как совокупность ячеек, в каждой из которых может быть записано одно из двух значений: 0 или 1, то есть один разряд двоичного числа. Существует несколько типов регистров, отличающихся видом выполняемых операций. Некоторые важные регистры имеют свои названия, например: сдвиговый регистр; счетчики; счетчик команд; регистр. ЭВМ состоит из огромного числа отдельных логических элементов, базирующих все её узлы и память. Все устройства ЭВМ (процессор, оперативная память, контроллеры и т.д.) состоят из типовых логических устройств (сумматоров, триггеров, регистров, шифраторов, дешифраторов), работающих на основании аппарата математической логики. 6 Чтобы они могли совместно работать, необходима их совместимость на уровне логических элементов. Если такая совместимость есть, то компьютер можно собрать из отдельных узлов, произведённых разными фирмами, специализирующимися на разработке и выпуске определённого вида устройств, что чаще всего и наблюдается на практике. IV. Постановка домашнего задания § 3.7.2; § 3.7.3 V. Постановка домашнего задания § 3.7.2; § 3.7.3 1) Построить СДНФ для Р и S по таблице истинности и упростить. 2)* Построить логическую схему одноразрядного сумматора в среде LogModel. 7