Выпускная квалификационная работа Выполнил: Петрыкин Д.А., ФРТК, 613 гр.

реклама

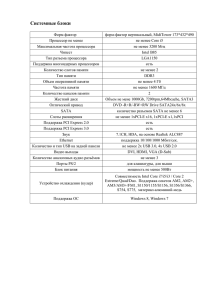

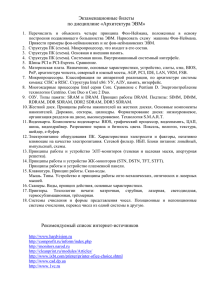

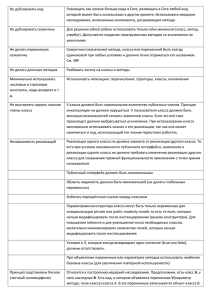

Выпускная квалификационная работа Выполнил: Петрыкин Д.А., ФРТК, 613 гр. Научный руководитель: Слесарев М.В. Схема кластера «Эльбрус-2S» 4 процессорных узла высокоскоростные межпроцессорные каналы LINK оперативная память вместе со справочником (directory) распределена между узлами Схема процессорного узла «Эльбрус-2S» 4 ядра кэш L2, L1 системный коммутатор (SC) 3 контроллера памяти 3 контроллера LINK контроллер ввода-вывода Поддержка когерентности данных на уровне кластера – механизм справочника на уровне процессорного узла – механизм snooping достоинства: - минимальная нагрузка на межпроцессорный трафик - относительно небольшой размер справочника недостатки: - уменьшение эффективного размера памяти - уменьшение эффективной пропускной способности канала в память - нагрузка на трафик внутри процессора Протокол MOSI 4 состояния кэш-строки Modified – строка модифицирована и в единственном экземпляре Owned – строка модифицирована и может быть у других ядер Shared – строка не модифицирована и может быть у других ядер Invalid – строка удалена справочник знает состояния строк во всей системе Реализация протокола MOSI состояние кэш-строки может измениться, если: 1. получен когерентный запрос 2. получен ответ на запрос 3. Coherent Invalidate (CI) Coherent Read (CR) Coherent Read & Invalidate (CRI) Invalidate (I) Read (R) Read & Invalidate (RI) Произошло вытеснение строки в память Write Back (WB) Схема протокола MOSI Состояния: M O S Запросы: CI CR CRI Ответы: I R RI События: store_hit store_miss I load_miss WB Обращение в память MEMORY MEMORY CORE CORE CORE CORE CORE SIC SIC CORE CORE CORE CORE CORE CORE CORE CORE CORE MEMORY SIC SIC CORE CORE MEMORY 4132 стадия: –– ядро-инициатор MAU HOMEядра отправляет каждое ядро отправляет Coherent Request Initial ответ Request только «нужным» в Response память обработчику Coherent процессорам (Short, Data) – завершающее просмотр Final в инициатору – сообщение состояний каждый процессор строки справочнике рассылает Coherent – Response ядро-инициатор Request своим – собирает и – строка «захват» строки ядрам «освобождается» анализирует ответы Постановка задачи Разработать устройство коммутации когерентных запросов и ответов со следующими функциями: приём когерентных запросов от 4 направлений мультиплексирование 4 входных каналов в 1 выходной одновременная рассылка запроса в L2 кэши всех ядер узла сбор и анализ ответов от всех ядер узла формирование короткого ответа отправка короткого ответа адресату Характеристики устройства Темп приема запросов и ответов на каждом входном канале: 1 запрос за такт Темп передачи запросов и ответов на каждом выходном канале: 1 запрос за такт Оптимальный темп приема snoop-запросов: 1 запрос за 4 такта (без учета блокировок) Частота: 1 ГГц (на технологии 65 нм) Замечание: не отправлять snoop-запросы подряд в один банк Варианты реализации 1. Использовать наработки из проекта «Эльбрус-S» коммутацию когерентных запросов выполнять в L2 кэше в буфере когерентных запросов – Coherent Request Buffer(CRB) все ответы собирать в MAU (Memory Access Unit) ядра-инициатора достоинства: - относительная простота - экономия времени недостатки: - увеличение оборудования на коммутацию запросов - существенное увеличение нагрузки на межпроцессорный трафик (т.к. в каждом процессоре 4 ядра) - либо существенное увеличение размера справочника Варианты реализации 2. Разработать устройство «с нуля» единый модуль (экономия межпроцессорного трафика, трафика внутри процессора, размера MAU и L2 кэша) фиксированное время обработки когерентного запроса с точностью до такта (позволяет избежать буфера ожидания ответов): – – – одновременный прием запросов в кэшах всех ядер одинаковое время обработки (установить максимальный приоритет) одновременный прием ответов из ядер Общая структура устройства Два модуля, связанные простым интерфейсом: Request Receiver – для коммутации запросов Response Collector – для приема ответов Request_Receiver: структура прием запросов от 4 устройств буферизация только для SC (т.к. в контроллерах LINK уже есть буфер) bypass, если FIFO пустое арбитр управляет мультиплексированием рассылка запросов ядрам (через фильтр) Response_Collector: структура прием ответов от MAU ядер и меток от Request Receiver обработка ответов и формирование короткого когерентного ответа 4 выходных канала (позволяют быстро разгрузить регистры после блокировки) отсутствие блокировки для канала SC, MAU Результаты разработки коммутатора когерентных запросов и ответов Проведен анализ ранних решений Разработан RTL устройства Разработано тестовое окружение Проведена отладка отдельных модулей Проведен предварительный анализ временных характеристик для отдельных модулей В настоящее время устройство проходит тестирование и отладку Спасибо за внимание!