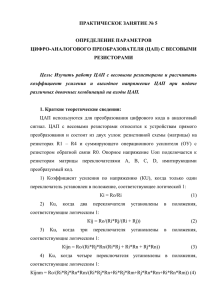

Калужский филиал МГТУ им. Н.Э. Баумана Кафедра систем автоматического управления Синтез комбинационных логических схем на основе методов многоуровневой декомпозиции Методы синтеза КЛС методы двухуровневого синтеза, предполагающие прохождение сигнала через два уровня логических элементов (как правило, это элементы «И», «ИЛИ», «НЕ» либо «И-НЕ» («ИЛИ-НЕ») методы многоуровневого синтеза, целью которого является синтез схемы в виде логической сети, удовлетворяющей заданным ограничениям Этапы двухуровневого синтеза КЛС Формальное описание поведения КЛС посредством таблицы истинности Получение СовНФ для всех собственных функций синтезируемой КЛС (СДНФ, СКНФ, СДИНФ, СКИНФ) Минимизация СовНФ с использованием аналитических или графических методов Переход к графическому изображению схемы на элементах «И», «ИЛИ», «НЕ», «И-НЕ», «ИЛИ-НЕ» Клод Шеннон Декомпозиционные методы синтеза КЛС позволяют получать многоуровневые представления логических функций являются наиболее общими методами логического синтеза Декомпозиционные методы синтеза КЛС Задача декомпозиции булевых функций является одной из важнейших в логическом синтезе, и в настоящее время известно большое число фундаментальных работ по этой тематике Разложение Шеннона f f ( xi 0) xi f ( xi 1) xi Публикации Публикации Публикации Публикации Публикации Особенности структуры современных ПЛИС FPGA КЛБ на простых логических вентилях («И- НЕ», «ИЛИ-НЕ») – Simple Logic Cells (SLC) КЛБ на основе мультиплексоров КЛБ на основе программируемых ПЗУ Loc-Up Tables) (LUT – КЛБ на элементах 2И-НЕ КЛБ на элементах 2И-НЕ КЛБ на элементах 2И-НЕ КЛБ на мультиплексорах КЛБ на мультиплексорах КЛБ на основе LUT Altera FLEX 8000A КЛБ на основе LUT Xilinx XC4000E Затраты ресурсов ПЛИС Всё многообразие цифровых логических схем принято делить на две большие группы: комбинационные логические схемы Всё многообразие цифровых логических схем принято делить на две большие группы: комбинационные логические схемы (КЛС) и автоматы с памятью, как правило, имеющие конечное число состояний (АП) Всё многообразие цифровых логических схем принято делить на две большие группы: комбинационные логические схемы Состояния сигналов на выходах комбинационных логических схем (КЛС) однозначно определяется только комбинацией состояний на входах схемы (отсюда и название такого класса схем) В отличие от КЛС, выходные сигналы автоматов зависят от состояния на входах и предыдущего внутреннего состояния схемы, то есть автомат обладает памятью (автомат с памятью – АП) Комбинационная логическая схема Входы n Исходная сложность схемы Выходы m n m 2 (бит). Структурно АП отличаются от комбинационных схем наличием обратных связей, что приводит к появлению свойств запоминания состояний. В каноническом представлении АП разделяются на две части: комбинационную логическую схему (КЛС) и память (П) x1 y1 xn ym КЛС q1 z1 qs zs П Таким образом, в конечном итоге, синтез автоматов так или иначе сводится к синтезу КЛС. В отличие от канонического представления автомат также может быть описан и реализован как комбинационная схема с обратными связями x1 y1 xn ym КЛС q1 z1 qs zs П Основными способами задания собственных функций КЛС являются таблицы истинности и алгебраические выражения Алгебраические формулы не являются инвариантными по отношению к базису, поэтому от такого способа следует отказаться Таблицы истинности инвариантны по отношению к базису, но достаточно громоздки и неудобны Числовая последовательность КЛС f1 (abc) abc abc abc abc f 2 (abc) ab ac bc a b c f2 f1 a b c f2 f1 0000 1111 0011 0011 0101 01 01 0001 0111 011 0 1 001 011 2 1 223 Числовая последовательность A0 A1 A2 ... Ai ... А(2n 1) индекс i i 1 2 n1 12 ... n 2 2 n 2 ... n 2 0 Обозначение входных переменных КЛС a (40 ) 0000 1111 b (20 ) 0011 0011 c (10 ) 0101 01 01 f 2 (2) 0001 0111 f1 (1) 0110 1001 011 2 1 223 40 20 10 f2 f1 Числовая последовательность не несёт никакой информации об именах аргументов логической функции Но для целей синтеза это не важно. Важен лишь порядок старшинства входных переменных, а этот порядок устанавливается весами соответствующих разрядов во входном двоичном наборе Поэтому аргументами мы будем считать весовые коэффициенты соответствующих им разрядов Указанное выше обозначение входных переменных исключает путаницу при синтезе и анализе схем, поскольку однозначно определяет место соответствующего аргумента во входном наборе и старшинство входов относительно друг друга Обозначение входных переменных КЛС a (40 ) 0000 1111 b (20 ) 0011 0011 c (10 ) 0101 01 01 f 2 (2) 0001 0111 f1 (1) 0110 1001 011 2 1 223 40 20 10 f2 f1 Числовая последовательность системы КЛС 0001 0111 0110 1001 0112 1223 Числовая последовательность системы недоопределённых функций 013* 1*23 Операции над числовыми последовательностями 1. Операции над аргументами логических функций 2. Операции над самими функциями Операции над числовыми последовательностями 1.1. Операция подстановки значения «0» вместо аргумента с весом p 0123 3322 3210 0011 20 0 (80 ,40 ,10 ) 0133 3200 80 40 20 10 f 0000 0000 1111 1111 0000 1111 0000 1111 0011 0011 0011 0011 0101 010 1 0101 0101 012 3 3322 3210 0011 Операции над числовыми последовательностями 1.2. Операция подстановки значения «1» вместо аргумента с весом p 0123 3322 3210 0011 20 1 (80 ,40 ,10 ) 2322 1011 Операции над числовыми последовательностями 1.3. Разложение числовой последовательности по переменной с весом p (80 ,40 ,10 ) 20 0133 3200 2322 1011 . Операции над числовыми последовательностями 1.3. Разложение числовой последовательности по переменной с весом p В общем виде матрица разложения строится следующим образом: ... a p a2 p1 ... a3 p ... p a1a2 a a ... a a ... a ... p 1 p 2 2 p 3 p 1 4 p ( p 0) ( p 1) Операции над числовыми последовательностями 1.4. Разложение числовой последовательности по инверсному значению переменной с весом p 20 2322 1011 . 0133 3200 Операции над числовыми последовательностями 1.5. Развёртывание матрицы разложения по переменной с весом p 20 0133 3200 . 2322 1011 0123 3322 3210 0011 Операции над числовыми последовательностями 1.6. Исключение фиктивной по переменной с весом p 2322 2322 1011 1011 40 2322 1011 . 2322 1011 (80 ,20 ,10 ) 2322 1011 Операции над числовыми последовательностями 1.6. Исключение фиктивной по переменной с весом p в случае недоопределённой логической функции 40 23** 1011 . 2 **2 1*11 (80 ,20 ,10 ) 23* 2 1011 Операции над числовыми последовательностями 1.7. Введение фиктивной переменной с весом p (40 ,20 ,10 ) 2312 1002 2312 1002 2312 1002 (80 ,40 ,20 ,10 ) 2323 1212 1010 0202 Операции над числовыми последовательностями 80 , 20 ,10 21 32 1.8. Разложение матрицы по переменной с весом q 21 (80 ,40 ,20 ,10 ) 2323 1212 1010 0202 32 80 , 20 2312 10 2312 80 2323 1212 02 1002 1010 0202 10 02 1002 Операции над числовыми последовательностями 1.9. Разложение числовой последовательности по двум переменным с весами p и q (q<p). В общем виде матрица разложения строится следующим образом: a a 1 2 p, q aq1 a p1 a pq1 ... aq a2 q 1 ... a2 q a3q 1 ... a pq ... a p2q ... a3q ... ... a4 q ... ... ... ... ... ( pq 00) ( pq 01) ( pq 10) ( pq 11) Операции над числовыми последовательностями 2.1. Разделение числовой последовательности на старшую и младшую составляющие Ai (1 2 n1 ... nk 1 2 ) ( nk 1 2 k k 1 2 Ai Ai p Ai Ai, k Ai - старшая составляющая числа A - младшая составляющая ... n 2 ) 0 Операции над числовыми последовательностями 2.1. Разделение числовой последовательности на старшую и младшую составляющие 6234 0567 1001 0111; 2230 0123. 1001 0111 1110 0011 0010 0101 Операции над числовыми последовательностями 2.2. Объединение числовых последовательностей 1 0 00 0111 2 2 21 0123 6221 0567 Операции над числовыми последовательностями 2.3. Логические операции над числовыми последовательностями 6234 0567 инверсия: 1543 7210 0110 1111 & 1111 1001 0110 1001 Задачи логического проектирования 1. Абстрактный синтез 2. Абстрактный анализ 3. Структурный синтез 4. Структурный анализ Структурный синтез схемы 1. Абстрактно-структурный синтез (декомпозиция) 2. Детализация 3. Покрытие заданными элементами 4. Оптимизация (на основе анализа) Декомпозиция логических схем 1. Параллельная декомпозиция 2. Последовательная декомпозиция 3. Параллельно-последовательная декомпозиция Исходное представление синтезируемой логической схемы Входы n Исходная сложность схемы Выходы m S0 m 2 (бит) n Критерий сложности синтезируемой логической схемы Исходная сложность схемы k S0 m 2 (бит) S Si (бит) i 1 n Уменьшение сложности описания схемы в результате декомпозиции a2 b2 b Pi 1 a pi 1 S а) 96 бит Pi 1 S2 a1 b1 pi 1 S1 б) 16+16=32 бита Двухразрядный двоичный сумматор Параллельная декомпозиция nk m1 k k Сложность схемы после разделения m2 S m1 2 m2 2 n k Условия выделения параллельного блока m1 2 m2 2 m2 ; n k n m2 2 (m m1 )2 2 2 ; k n kn k n Пример параллельной декомпозиции 40 20 10 A B Пример параллельной декомпозиции 0112 0113 0101 1 213 0101 1 213 40 20 10 A 0 1 1 B 1 1 1 Пример параллельной декомпозиции 40 20 0110 0111 B 10 1 0001 A 2 0112 0113 0001 0001 ( A) 0110 0111 ( B) 0001 0001 Последовательная декомпозиция nk m k l Сложность схемы после разделения S l 2 m2 k nk l Условия выделения последовательного блока l 2 m2 k n k l m2 ; l 2 m(2 2 k n n n k l l 2 m2 (1 2 k n lk l k ); ); Пример последовательной декомпозиции 80 40 20 10 0001 1111 0011 1111 Пример последовательной декомпозиции 20 ,10 0101 0101 0111 1111 40 ,10 0001 0101 1111 1111 40 ,20 0000 0111 1111 1111 80 ,10 0011 0 0111 1 0111 1 0111 1 Пример последовательной декомпозиции 41 21 11 40 20 80 10 0001 1111 0111 C 0011 8010 0111 Пример последовательной декомпозиции 0001 1111 21.11 01 01 01 11 C 0 2111 1 1 1 0 0 0 1 41 21 11 0111 0001 Пример последовательной декомпозиции 0111 40 C 20 80 10 B A 0001 0111 Сложность схемы 12 бит Пример синтеза рассматриваемой схемы с использованием карт Карно 2 1 1 8 1 1 1 1 1 1 1 1 1 1 4 f 40 80 20 10 20 Пример синтеза рассматриваемой схемы с использованием карт Карно 80 20 & 1 40 & 10 Сложность схемы 16 бит Пример синтеза рассматриваемой схемы с использованием карт Карно f 40 20 (80 10 ) 1 40 & 20 80 10 1 Параллельно-последовательная декомпозиция nk m1 k l m2 Объединение блоков при параллельнопоследовательной декомпозиции nk m1 l k m2 Объединение блоков при параллельнопоследовательной декомпозиции nk m1 l k m2 Декомпозиция проводится до тех пор, пока существует возможность разделения блоков с соблюдением неувеличения критерия сложности описания синтезируемой схемы В результате получается блок-схема проектируемого устройства Алгоритм декомпозиции: 1. Выделение параллельного блока 2. Выделение последовательного блока с теми же входами 3. Объединение выделенных блоков Структурный анализ логических схем Структурный анализ логических схем 0111 40 C 20 80 10 B A 0111 0001 Последовательность на выходе блока 1 яруса 80 0000 0000 1111 1111 10 0101 0101 0101 0101 A 0101 0101 1111 1111 . Последовательность на выходе блока 2 яруса 20 0011 0011 0011 0011 A 0101 0101 1111 1111 B 0001 0001 0011 0011 . Последовательность на выходе блока 3 яруса 40 0000 1111 0000 1111 B 0001 0001 0011 0011 C 0001 1111 0011 1111 . Пример синтеза разряда двоичного сумматора по модулю 4 bi ai pi 1 160 80 Р 40 S 2 20 S1 10 S0 3 2 96 5 pi 1 si Абстрактный синтез Si ai bi pi1 bi pi 1 ai 0 ai 1 ai 2 ai 3 0 0 1 1 0 1 0 1 0 1 1 2 1 2 2 3 2 3 3 4 3 4 4 5 2 2 3 3 0 1 0 1 2 3 3 4 3 4 4 5 4 5 5 6 5 6 6 7 Числовая последовательность сумматора по модулю 4 0112 2334 1223 3445 2334 4556 3445 5667 Поиск фиктивных входных переменных 0112233412233445 2334455634455667 011 2233423344556 1223344534455667 0112122323343445 2334344545565667 01 231 23423453456 1234234534564567 01 231 23423453456 1234234534564567 Таблица результатов анализа фиктивной зависимости выходов от входов 160 80 40 20 10 P 1 1 1 1 1 S2 1 1 1 1 1 S1 0 1 0 1 1 Параллельная декомпозиция сумматора 160 80 40 20 10 Р S2 1 S1 2 Числовая последовательность блока 2 0110 0110 1001 1001 0110 0110 1001 1001 40 01101001 01101001 01101001 01101001 . 0110 1001 Числовая последовательность блока 1 0001 1112 0111 1222 1112 2223 1222 2333 Сложность схемы после разделения 2 2 1 2 72 (бит) 5 3 Выделение последовательного блока 80 ,20 ,10 011 2 011 2 011 2 1 223 011 2 1 223 1 223 1 223 . Р 160 40 4 80 20 10 S2 3 S1 2 2(1 2 ) 2 2 32 (бит) 3 3 Последовательность блока 3 0001 0111 Последовательность блока 4 C 011 2 ,20 ,10 1223 . 0112 1223 Структурная схема разряда двоичного сумматора по модулю 4 Р 160 40 80 20 10 4 41 21 11 23 S2 S1 Параллельная декомпозиция сумматора по модулю 2 (0112 1223) 41 0112 21 0112 1223 ; 1223 ; P S 41 1 1 21 1 1 11 0112 1123 11 1 1 Последовательная декомпозиция сумматора по модулю 2 (0112 1223) 21,11 01 12 ; 12 23 41,11 01 12 ; 12 23 41,21 01 12 . 12 23 Структурная схема разряда двоичного сумматора по модулю 4 SM 160 (ai 2 ) 40 (bi 2 ) 2 80 (ai1 ) SM 1 P( pi 1 ) S S 2( s2 ) P 20 (bi1 ) 10 ( pi 1 ) P S S1( s1 ) Анализ схемы двоичного сумматора по модулю 4 Числовые последовательности на входах блока 1 0000 0000 1111 1111 0000 0000 1111 1111 0011 0011 0011 0011 0011 0011 0011 0011 0101 0101 0101 0101 0101 0101 0101 0101 Анализ схемы двоичного сумматора по модулю 4 Последовательность на выходах блока 1 80 0000 0000 1111 1111 0000 0000 1111 1111 20 0011 0011 0011 0011 0011 0011 0011 0011 10 0101 0101 01 01 01 01 0101 0101 01 01 01 01 SM 1 011 2 011 2 1 223 1 223 011 2 011 2 1 223 1 223 . Анализ схемы двоичного сумматора по модулю 4 Последовательность на выходах блока 2 160 0000 0000 0000 0000 1111 1111 1111 1111 40 0000 1111 0000 1111 0000 1111 0000 1111 P1 0001 0001 0111 0111 0001 0001 0111 0111 SM 2 0001 111 2 0111 1 222 111 2 2223 1 222 2333 . Анализ схемы двоичного сумматора по модулю 4 Последовательность на выходах сумматора SM 22 SM 21 SM1 SM 4 0000 000 1 0000 0 111 000 1 1111 0 111 1111 000 1 1110 0 111 1000 1110 0001 1000 0111 0110 0110 1001 1001 0110 0110 1001 1001 0112 2 334 122 3 3445 2 334 4556 3445 5667 . Исследование зависимости выходов от входов 10 20 40 80 160 320 640 1280 2560 P 1 1 1 1 1 1 1 1 1 S8 1 1 1 1 1 1 1 1 1 S4 1 1 1 1 0 1 1 1 0 S2 1 1 1 0 0 1 1 0 0 S1 1 1 0 0 0 1 0 0 0 Выделение параллельного блока 2560 1280 640 320 160 80 40 20 10 P S8 S4 A S2 S1 B Определение последовательности блока B 2560 ,1280 ,160 ,80 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 0112 2330 1223 3001 2330 0112 3001 1223 Определение последовательности блока B 0112 2330 1223 3001 2330 0112 3001 1223 Выделение последовательного блока из блока A 2560 ,1280 ,160 ,80 0000 0001 0000 0111 0001 1111 0111 1111 1111 1112 1111 1222 1112 2222 1222 2222 2222 2223 2222 2333 2223 3333 2333 3333 3333 3334 3333 3444 3334 4444 3444 4444 1111 1112 1111 1222 1112 2222 1222 2222 2222 2223 2222 2333 2223 3333 2333 3333 3333 3334 3333 3444 3334 4444 3444 4444 4444 4445 4444 4555 4445 5555 4555 5555 2222 2223 2222 2333 2223 3333 2333 3333 3333 3334 3333 3444 3334 4444 3444 4444 4444 4445 4444 4555 4445 5555 4555 5555 5555 5556 5555 5666 5556 6666 5666 6666 3333 3334 3333 3444 3334 4444 3444 4444 4444 4445 4444 4555 4445 5555 4555 5555 5555 5556 5555 5666 5556 6666 5666 6666 6666 6667 6666 6777 6667 7777 6777 7777 Определение последовательности блока B 2560 1280 160 80 P S8 D 640 320 40 20 10 S4 C 0000 0001 0000 0111 0001 1111 0111 1111 Объединение блоков B и С 2560 1280 160 80 P S8 D 640 320 40 20 10 161 1 81 41 2 21 3 11 BC S4 S2 S1 0000 0001 0000 0111 0001 1111 0111 1111 Определение последовательности блока BС 0000 0001 0000 0111 0001 1111 0111 1111 0112 2330 1223 3001 2330 0112 3001 1223 0112 2334 1223 3445 2334 4556 3445 5667 Определение последовательности блока D 2560 ,1280 ,160 ,8C0 01 12 23 34 12 23 34 45 23 34 45 56 34 45 56 67 0112 2334 1223 3445 2334 4556 3445 5667 Параллельная декомпозиция блока BС 161 81 41 21 11 1 2 E 3 F 161 41 0110 1001 0110 1001 0110 1001 0110 1001 Последовательная декомпозиция блока E 161 41 1 H 81 21 11 161 41 0001 0111 1112 1222 1112 1222 2223 2333 2 G 161 41C 01 12 12 23 0112 1223 Объединение блоков F и G 161 41 1 H 81 21 11 2 3 FG 0001 0111 011 0 1 001 011 2 1 223 Схема разряда двоичного сумматора по модулю 16 SM 2560 (ai8 ) P P( pi 1 ) S S 8( s8 ) 160 (bi8 ) SM 1280 (ai 4 ) 80 (bi 4 ) S SM 640 (ai 2 ) 40 (bi 2 ) 320 (ai1 ) SM S 4( s4 ) P S S 2( s2 ) P 20 (bi1 ) 10 ( pi 1 ) P S S1( s1 )