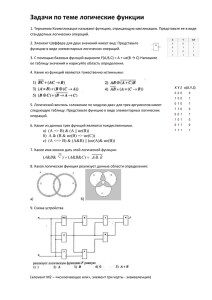

1 Комбинационные логические схемы • Схема является комбинационной, если: • ее состояние зависит только от текущих состояний входов (схема «не помнит» предыдущее состояние); • каждый элемент схемы сам является комбинационным; • вход любого элемента имеет только один источник сигнала (за исключением выходов элементов с третьим состоянием); • схема не содержит обратных связей. 2 Основные логические элементы • На основе базового набора логических элементов – И (AND), ИЛИ (OR), НЕ (NOT) – может быть построена комбинационная схема любой сложности. • NAND – И-НЕ • NOR – ИЛИ-НЕ • XOR – Исключающее ИЛИ • MUX2 – Мультиплексор 2 в 1 3 Синтез логических схем Булева алгебра Описание Теорема Обратная теорема Операции с 0 и 1 B•1=B B+0=B B•0=0 B+1=1 Правило повторения B•B=B B+B=B Правило дополнения B • B¯ = 0 B + B¯ = 1 Двойное отрицание B¯ ¯= B Коммутативность B•C=C•B B+C=C+B Ассоциативность (B • C) • D = B • (C • D) (B + C) + D = B + (C + D) Дистрибутивность (B • C) + (B • D) = B • (C + D) (B + C) • (B + D) =B + (C • D) Поглощение B • (B + C) = B B + (B • C) = B Склеивание (B • C) + (B • C¯ ) = B (B + C) • (B + C¯ ) = B • Теорема Двойственная теорема Название 4 Булева алгебра в схемотехнике 5 • Элемент И-НЕ эквивалентен элементу ИЛИ с инверсными входами. • Аналогично, ИЛИ-НЕ эквивалентен элементу И с инверсными входами. 6 Синтез логических схем • Таблица истинности –> ДНФ –> минимизация полученной логической функции –> приведение к стандартному элементному базису И-НЕ, ИЛИ-НЕ • Таблица истинности –> ДНФ –> программируемая логическая матрица (ПЛМ) • Таблица истинности –> запоминающее устройство, в которое записывается таблица истинности (такой подход используется в программируемых логических интегральных схемах) 7 8 Реализация логических функций с помощью стандартных логических элементов 9 Задержка распространения сигнала в логических схемах 10 Возникновение помехи в комбинаторной логике 11 Реализация логических функций с помощью ПЛМ • Программируемая логическая матрица (ПЛМ) представляет собой специализированную микросхему, которая содержит в своем составе две логических матрицы «И» и «ИЛИ». Матрица И необходима для получения элементарных конъюнкций от входных сигналов, а матрица ИЛИ - объединяет полученные произведения. 12 Буферный усилитель с тремя состояниями • • • • • Третье состояние (Z) – выход отключен или находится в состоянии высокого сопротивления Основное назначение – объединение выходов нескольких устройств на общей шине данных Если вход управления En = 0, то выход соответствующего устройства отключается от общей шины и устройство может принимать данные Если Еn=1 устройство может передавать данные на общую шину В каждый момент времени на общей шине может быть только один передатчик! 13 Пример разработки: Мультиплексор 4 в 1 реализация с помощью ПЛМ (a), буферных усилителей с третьим состоянием (b), мультиплексоров 2 в 1 (c) 14 • Замечание. Для построения мультиплексора 4 в 1 на основе буферных усилителей с третьим состоянием, нам потребуется еще и дешифратор 2 в 4 15 Сравнение задержек в мультиплексорах 16 Микросхемы средней степени интеграции серии 54/74 74aaXXX 00 02 Функциональное назначение 4 элемента NAND2 4 элемента NOR2 2 элемента NAND4 2 элемента AND4 • • Двоично-десятичный дешифратор • ... 20 21 ... 42 ... 48 Дешифратор-драйвер 7-сегм. индикатора ... 68 4-х разрядный двоичный счетчик ... 99 4-х разрядный сдвиговый регистр • ... 150 Мультиплексор на 16 каналов со стробированием ... 201 256-bit (256x1) RAM ... 283 4-х разрядный полный сумматор ... 462 Передатчик ВОЛС (fiber-optic link) • Например: SN74ALS245 SN – производитель (Texas Instruments), серия микросхем: 74 - коммерческое исполнение (от 0°C до 70°C), 54 - индустриальное (от –55°C до 125°C) ALS – тип логики (в данном случае ТТЛШ с низким энергопотреблением), 245 – функциональное назначение (восьмибитный двунаправленный буфер). 17 Пример: Дешифратор двоично-десятичного кода в позиционный десятичный