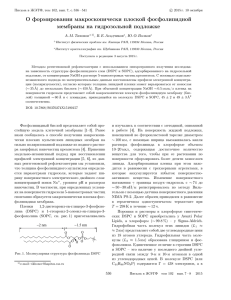

Лекция 5. NIOS II Nios II это 32-разрядная микропроцессорная архитектура для встраиваемых приложений (Soft-микропроцессор), разработанная специально для ПЛИС фирмы Altera. Nios II является развитием архитектуры Nios и находит применение в различных встраиваемых приложениях, начиная от цифровой обработки сигналов до управляющих систем. Nios II можно сравнить с MicroBlaze, конкурирующей микропроцессорной архитектурой для ПЛИС фирмы Xilinx. В отличие от Microblaze, Nios II возможно лицензировать для реализации в СБИС при посредничестве Synopsys Designware В этой лекции описывается полный процесс разработки для создания системы Nios II и прототипирования еѐ на выбранной плате. На рисунке 5.1 показан процесс разработки системы Nios II. Рисунок 5.1 – Процесс разработки Процесс разработки начинается с рассмотрения проекта как такового, включая анализ требований к приложению, отвечающий на следующие вопросы: ■ Какие вычислительные характеристики требуются в приложениях? ■ Какая полоса пропускания или производительность требуется в приложениях? ■ Такие типы интерфейсов требуются в приложениях? ■ Требуется ли многопоточное программное обеспечение в приложениях? Основываясь на ответы на эти вопросы, вы можете конкретизировать системные требования, такие как: ■ Какое ядро процессора Nios II использовать: малое или быстрое. ■ Какие компоненты понадобятся и сколько конкретно каждого типа. ■ Какую операционную систему реального времени (RTOS), если нужно. ■ Какая логика ускорения аппаратных средств может существенно улучшить характеристики системы. Например: ■ Может ли компонент DMA устранить пустые процессорные циклы копирования данных? ■ Могут ли специальные инструкции переместить критические петли DSP алгоритма? Для анализа этих требований необходимо задействовать группы разработчиков аппаратных и программных средств. Определение и генерирование системы в SOPC Builder После анализа требований к аппаратной части системы, необходимо использовать SOPC Builder для определения ядра (ядер) процессора Nios II, памяти и прочих компонентов, необходимых в вашей системе. SOPC Builder автоматически генерирует логику внутренних соединений для интегрирования компонентов в аппаратную часть системы. Можно выбрать из списка стандартных ядер процессора и компонентов, предлагаемых в Nios II EDS. Также можно добавить свои собственные аппаратные компоненты для ускорения характеристики системы. Вы можете добавить логику собственных инструкций для ядра Nios II, которая улучшает характеристики CPU, или добавить собственных компонент, разгружающий CPU от задач. Главной задачей SOPC Builder является получения следующих типов файлов: ■ Файл проекта SOPC Builder (.sopc) — Содержит аппаратную часть системы SOPC Builder. ■ Файл информации SOPC Builder (.sopcinfo) — Содержит удобочитаемое описание содержимого файла .sopc. Nios II EDS использует файл .sopcinfo для компиляции программного обеспечения для выбранного устройства. ■ Файлы языка описания аппаратуры (HDL) – Все файлы проектирования аппаратных средств, описывающих систему SOPC Builder. Программа Quartus II использует HDL файлы для компиляции всего проекта FPGA в выходной файл SRAM (.sof). За подробной информацией о ядрах процессора Nios II, обратитесь к Настольной книге процессора Nios II. За подробной информацией о SOPC Builder и разработке собственных компонентов, обратитесь к тому 4: SOPC Builder в книге Quartus II. За подробной информацией о собственных инструкциях, обратитесь к Руководству пользователя собственных инструкций Nios II. Эту литературу можно свободно скачать из сети Интернет. Интегрирование системы SOPC Builder в проект Quartus II После генерирования системы Nios II с использованием SOPC Builder, вы интегрируете его в проект Quartus II. Используя программу Quartus II, вы выполняете все задачи, необходимые для создания конечного аппаратного проекта FPGA. Как показано на рисунке 5.1, большинство проектов FPGA имеют логику, строящуюся вокруг системы Nios II. Вы можете интегрировать свои собственные аппаратные модули в проект FPGA или другие готовые модули проекта, защищѐнные авторским правом (IP), поставляемые Altera или другими IP разработчиками. Используя программу Quartus II, вы можете также назначить размещение выводов для I/O сигналов, определить временные ограничения и прочие ограничения для проекта. В завершении, вы компилируете проект Quartus II, чтобы получить .sof файл для конфигурирования FPGA. Вы загружаете .sof файл в FPGA на выбранной плате с помощью загрузочного кабеля, например USB-Blaster. После конфигурирования, FPGA преобразуется в специальный аппаратный проект, в нашем случае это система с процессором Nios II. Разработка программного обеспечения с помощью инструмента создания программы Nios II под Eclipse Используя инструмент создания программы Nios II под Eclipse, вы выполните все задачи разработки программного обеспечения для вашей системы с процессором Nios II. После того, как вы сгенерируете систему с помощью SOPC Builder, вы можете сразу же начать разработку вашего C/C++ программного кода с помощью инструмента создания программы Nios II под Eclipse. Altera поставляет драйверы компонентов и уровень аппаратных абстракций (HAL), позволяющие вам быстро писать программы для Nios II, не зависимо от низкоуровневых особенностей аппаратных средств. В дополнении в вашему программному коду, вы можете разрабатывать и использовать собственные библиотеки в ваших проектах с помощью инструмента создания программы Nios II под Eclipse. Для создания нового проекта приложения Nios II C/C++, инструмент создания программы Nios II под Eclipse использует информацию из .sopcinfo файла. Вам также необходим .sof файл для конфигурирования FPGA перед запуском и отладкой прикладного проекта в выбранном устройстве. Инструмент создания программы Nios II под Eclipse может создать несколько выходных файлов, описанных ниже. Не всем проектам требуется всѐ перечисленное ниже: ■ Файл system.h – определяет идентификатор для обращения к аппаратной части системы. Инструмент создания программы Nios II под Eclipse автоматически создаѐт этот файл, когда вы создаѐте новый проект. ■ Файл формата исполнения и связи (.elf) — это результат компиляции проекта приложения C/C++, который вы загружаете прамо в процессор Nios II. ■ Шестнадцатеричный файл (формат Intel) (.hex) — содержит информацию об инициализации памяти на чипе. Инструмент создания программы Nios II под Eclipse генерирует эти файлы инициализации для памяти на чипе, поддерживающей инициализацию содержимого. ■ Данные для программирования флеш-памяти – это код самозагрузки и другие произвольные данные, которые вы должны загрузить во флеш-память. Инструмент создания программы Nios II под Eclipse имеет флеш-программатор, который позволяет вам записывать вашу программу во флеш-память. Флеш-программатор добавляет соответствующий загрузочный код, позволяя вам запрограммировать загрузку из флешпамяти. Вы можете также использовать флеш-программатор для записи нужных данных во флеш-память. Запуск и отладка программы в выбранной плате Инструмент создания программы Nios II под Eclipse предоставляет полный набор средств для загрузки программы в выбранную плату, запуска или отладки программы в устройстве. Инструмент создания программы Nios II под Eclipse позволяет вам запускать и останавливать процессор, пошагово исполнять код, устанавливать точки останова и анализировать переменные по ходу выполнения программы. Итерационное создание системы Nios II Большинство технологий создания комплексных систем Nios II начинают с простой системы SOPC Builder, затем итерационно прибавляют к ней дополнительные модули. На каждой итерации, вы можете проверить правильность функционирования системы. Вы можете выбрать верификацию основных компонентов системы: процессора, памяти и каналов коммутации, прежде чем добавлять прочие комплексные компоненты. Когда разрабатывается собственный компонент или собственная инструкция, то сначала нужно интегрировать собственную логику в минимальную систему, чтобы проверить еѐ функционирование, а затем вы можете интегрировать собственную логику в более комплексную систему. Intel (Altera) предлагает несколько базовых рабочих проектов Nios II, которые вы можете использовать в качестве начальной точки для своего собственного проекта. После инсталляции Nios II EDS, обратитесь к директории <Nios II EDS путь установки >/examples/verilog или к <Nios II EDS путь установки >/examples/vhdl. Демонстрация приложений также доступна при инсталляции в новых наборах разработчика. Верификация системы с помощью инструментов симуляции аппаратных средств Вы можете выполнить симуляцию аппаратных средств или исполнение программы в системе Nios II, используя инструменты, такие как RTL симулятор ModelSim®. Аппаратная симуляция прекрасно подходит для получения точных требований, включая следующие случаи: ■ Для верификации точных циклических характеристик системы Nios II прежде, чем будет доступна аппаратная часть. ■ Для верификации функционирования собственных компонентов или собственных инструкций Nios II прежде, чем испытывать их в аппаратной части. Часть с аппаратной симуляцией не показана на рисунке 5.1. Если вы создали систему Nios II, основываясь на стандартных компонентах, предлагаемых в Nios II EDS, то самый простой путь для функциональной верификации – это загрузка аппаратной и программной частей непосредственно в плату разработки. За подробной информацией о выполнении аппаратной симуляции системы Nios II, можно обратиться к AN351: Симуляция проектов со встроенным процессором Nios II. Инсталляция файлов проекта Прежде чем начать, вы должны установить программу Quartus II и Nios II EDS. Также необходимо загрузить учебный проект с веб-сайта Intel (Altera). Файлы проекта позволяют использовать готовый проект Quartus II в качестве отправной точки. Выполните следующие пункты для установки среды разработки: 1. Найдите заархивированные файлы проекта на веб-сайте Intel(Altera). 2. Разархивируйте содержимое архива в директорию на вашем компьютере. Не используйте пробелы в имени директории. Анализ требований к системе В этой секции описаны системные требования для примера учебного проекта. Пример проекта преследует следующие цели: ■ Демонстрация простой системы с процессором Nios II, которую вы можете использовать для контрольных приложений. ■ Практическое создание реальной системы, в процессе получения учебного опыта. ■ Демонстрация большинства общих и эффективных методик практического построения собственной системы Nios II. ■ Построение системы Nios II, способной работать на некоторых платах с установленной InteAltera FPGA. Эта система должна использовать только внутри чиповые ресурсы и не зависеть от выбранной платы. ■ Проект должен сохранять внутри чиповую логику и память так, чтобы иметь возможность быть размещѐнным в широком диапазоне чипов FPGA. Выполнение этих задач приводит к следующим проектным решениям: ■ Система Nios II использует только следующие входы и выходы: ■ Один тактовый вход постоянной частоты; ■ Восемь опциональных выходов для контрольных светодиодов на выбранной плате. ■ Проект использует следующие компоненты: ■ Ядро Nios II/s с кэшем инструкций 2 Кб; ■ 20 Кб памяти на чипе; ■ Таймер; ■ JTAG UART; ■ Восемь параллельных выходных выводов I/O (PIO); ■ Компонент идентификации системы. Запуск программы Quartus II и открытие примера проекта Для начала, вы открываете проект Quartus II для примера учебного проекта. Этот проект Quartus II служит простой отправной точкой процесса разработки Nios II. Проект Quartus II содержит все настройки и файлы проекта, необходимые для создания .sof файла. Для открытия проекта Quartus II выполните следующие пункты: 1. Запустите программу Quartus II. На Windows компьютерах кликните Пуск, выберите Программы, Altera, Quartus II <версия>, а затем кликните на Quartus II <версия>. На Linux компьютерах, введите quartus в командной строке, учитывайте директорию программы Quartus II в пути поиска. 2. В меню Файл, кликните Открыть проект. Раскроется диалоговое окно Открыть проект. 3. Найдите <директорию файлов проекта>. 4. Выберите файл nios2_quartus2_project.qpf и кликните Открыть. 5. Если программа Quartus II не отображает автоматически файл блок-схемы (.bdf) nios2_quartus2_project.bdf (Рисунок 1–3), выполните следующее: a. В меню Файл кликните Открыть, раскроется диалоговое окно Открыть. b. Найдите <директорию файлов проекта>. c. Выберите файл nios2_quartus2_project.bdf и кликните Открыть. На рисунке 5.2 показан файл nios2_quartus2_project.bdf. Рисунок 5.2 – Окно проекта Файл .bdf содержит входной вывод для такта и восемь выходных выводов для управления светодиодами на плате. Далее мы создадим систему SOPC Builder, которая непосредственно подключается к этим выводам. Создание новой системы SOPC Builder Для генерирования системы Nios II используется SOPC Builder, добавляющий нужные компоненты и конфигурирующий взаимосвязи между ними. Выполните следующие пункты для создания новой системы SOPC Builder: 1. В меню Инструменты программы Quartus II кликните SOPC Builder. Запустится SOPC Builder и отобразится диалоговое окно Создать новую систему. 2. Введите в качестве Имени системы first_nios2_system. 3. Выберите Verilog или VHDL в качестве Выбираемого HDL. Если вам всѐ равно, оставьте по умолчанию. Позже, когда будет сгенерирована система, вы выберите выходные файлы проекта SOPC Builder. 4. Кликните ОК. Откроется SOPC Builder, отображается вкладка Содержание системы. На рисунке 5.3 показано начальное состояние графической оболочки SOPC Builder. Рисунок 5.3 – Начальное окно SOPC Builder Вы используете SOPC Builder для определения характеристик аппаратной части системы Nios II, например, какое ядро Nios II использовать, и какие компоненты входят в систему. SOPC Builder не определяет поведение программной части, например, какая память используется для хранения инструкций, или как передать поток символов stderr. В этой секции вы выполните следующие пункты: 1. Выбор FPGA и настроек тактового сигнала. 2. Добавление ядра Nios II, внутри чиповой памяти и прочих компонентов. 3. Определение базового адреса и приоритета запроса прерываний (IRQ). 4. Генерирование системы SOPC Builder. Процесс разработки SOPC Builder не обязательно линеен. Пошаговое проектирование в этом учебном пособии представляет общий прямолинейный порядок, понятный начинающим пользователям. Таким образом, вы можете выполнять пункты проектирования системы SOPC Builder в любом порядке. Выбор FPGA и настроек тактового сигнала Секции Исполнитель и Настройки тактового сигнала на вкладке Содержание системы определяют взаимодействие системы SOPC Builder с другими устройствами в системе. Выполните следующие пункты: 1. Выберите Семейство чипов из производимых Altera FPGA, которое вы будете использовать. Если появляется предупреждение, что выбранное семейство чипов не существует в проекте Quartus, проигнорируйте это предупреждение. Вы можете выбрать чип позже в настройках проекта Quartus. 2. В документации на отладочную плату, обратите внимание на частоту сигнала тактового генератора, поступающую на FPGA. Руководство пользователя платой разработчика Altera находится на странице Литература: Наборы разработчика на веб-сайте Altera. 3. Дважды кликните на тактовую частоту в столбце МГц для clk_0. В системе SOPC Builder clk_0 – это имя тактового сигнала по умолчанию. Частота, введѐнная вами для clk_0, должна соответствовать частоте, поступающей от генератора на FPGA. 4. Введите частоту и нажмите Ввод. Далее вы начнѐте добавлять компоненты в систему SOPC Builder. После добавления каждого компонента, вы можете его сконфигурировать в соответствии со спецификацией проекта. Добавление внутри чиповой памяти Процессорным системам требуется не менее одной памяти под данные и инструкции. Этот пример проектирования использует одну память на чипе 20 Кб под данные и инструкции. Для добавления памяти выполните следующие пункты: 1. В списке доступных компонентов (с левой стороны на вкладке Содержимое системы), раскройте Память и контроллеры памяти, раскройте На чипе, затем кликните на Внутри чиповая память (RAM или ROM). 2. Кликните Добавить. Раскроется интерфейс MegaWizard для внутри чиповой памяти (RAM или ROM). На рисунке 5.4 показан его графический интерфейс. 3. В списке Тип блока выберите Автоматически. 4. На панели Общий размер памяти, введите 20 и выберите Килобайт, чтобы определить память размером 20 Кб. 5. Не меняйте никакую настройку по умолчанию. Рисунок 5.4 – Окно добавления памяти 6. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а внутри чиповая память сразу появится в таблице доступных компонентов. Чтобы подробнее изучить внутри чиповую память, вы можете кликнуть на Документацию в интерфейсе MegaWizard для внутричиповой памяти (RAM или ROM). Такая документация доступна для каждого компонента в интерфейсе MegaWizard/ 7. Правым кликом на внутри чиповую память выберите Переименовать. 8. Введите onchip_mem и нажмите Ввод. Добавление ядра процессора Nios II В этой секции вы добавите ядро Nios II/s и сконфигурируете его для использования 2 Кб внутри чиповой памяти под кэш инструкций. По замыслу обучения, пример учебного проекта использует "стандартное" ядро Nios II/s, которое является сбалансированным компромиссом между характеристиками и использованием ресурсов. Реально, ядро Nios II/s более мощное, чем требуется для большинства контрольных приложений. Выполните следующие пункты для добавления ядра Nios II/s в вашу систему: 1. В списке доступных компонентов, раскройте Процессоры, затем кликните Процессоры Nios II. 2. Кликните Добавить. Раскроется интерфейс MegaWizard для процессоров Nios II, отображающий страницу Ядра Nios II. На рисунке 5.5 показана графическая оболочка. 3. Под Выбрать ядро Nios II выберите Nios II/s. 4. В списке Аппаратное умножение выберите Нет. 5. Выключите Аппаратное деление. 6. Под Вектором сброса выберите onchip_mem в списке Память и введите 0x0 в панели Начальный номер (Офсет). 7. Под Вектором исключения выберите onchip_mem в списке Память и введите 0x20 в панели Начальный номер (Офсет). Рисунок 5.5 – Добавление ядра процессора 8. Кликните Интерфейсы с памятью и кэшем. Раскроется страница Интерфейсы с памятью и кэшем. На рисунке 5.6 показан его графический интерфейс. 9. В списке Кэш инструкций выберите 2 Кбайта. 10. Выключите Разрешить пакеты. 11. Выключите Содержит прочно сопряжѐнные инструкции для мастер порта (-ов). Рисунок 5.6 – Окно «Интерфейсы» 12. Не меняйте никакие настройки на страницах Расширенные средства, Настройки MMU и MPU, Модуль отладки JTAG и Собственные инструкции. 13. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а модуль ядра Nios II сразу появится в таблице доступных компонентов. SOPC Builder автоматически подключит мастер порты инструкций и данных ядра Nios II к ведомому порту памяти. На рисунке 5.7 показан графический интерфейс. Когда строится система, всегда контролируйте, что SOPC Builder автоматически подключает в соответствии с требованиями вашей системы. Рисунок 5.7 – Графический интерфейс SOPC Builder Добавление JTAG UART JTAG UART – это простой путь обмена символьными данными с процессором Nios II посредством загрузочного кабеля USB-Blaster. Выполните следующие пункты для добавления JTAG UART: 1. В списке доступных компонентов раскройте Протоколы интерфейса, затем Последовательный, и кликните JTAG UART. 2. Кликните Добавить. Раскроется интерфейс MegaWizard для JTAG UART. На рисунке 5.8 показан графический интерфейс. 3. Не меняйте настройки по умолчанию. Рисунок 5.8 – Настройка JTAG 4. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а модуль JTAG UART сразу появится в таблице доступных компонентов. SOPC Builder автоматически подключит мастер порт данных ядра Nios II к ведомому порту JTAG UART. (Мастер порт инструкций не может подключаться к JTAG UART, поскольку JTAG UART – это не устройство памяти и не может следовать инструкциям процессора Nios II). Когда строится система, всегда контролируйте, что SOPC Builder автоматически подключает в соответствии с требованиями вашей системы. Добавление интервального таймера Большинство контрольных систем используют компонент таймера, чтобы разрешить точный подсчѐт времени. Чтобы создать периодический такт системных часов, Nios II HAL обращается к таймеру. Выполните следующие пункты для добавления таймера: 1. В списке доступных компонентов раскройте Периферия, затем Периферия микроконтроллера, и кликните Интервальный таймер. 2. Кликните Добавить. Раскроется интерфейс MegaWizard для интервального таймера. На рисунке 5.9 показан графический интерфейс. 3. В списке Предустановка, выберите Полнофункциональный. 4. Не меняйте настройки по умолчанию. Рисунок 5.9 – Настройка таймеров 5. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а модуль интервального таймера сразу появится в таблице доступных компонентов. 6. Правым кликом на интервальном таймере выберите Переименовать. 7. Введите имя sys_clk_timer и нажмите Ввод. За дополнительной информацией о таймере, обратитесь к главе "Ядро таймера" в томе 5 Настольной книге процессора Quartus II". Добавление периферии идентификатора системы Периферия идентификатора системы защищает от случайной загрузки программы, скомпилированной для другой системы Nios II. Если в системе присутствует периферия идентификатора системы, инструмент создания программы Nios II под Eclipse предотвращает загрузку программы, скомпилированной для другой системы. Выполните следующие пункты для добавления периферии идентификатора системы: 1. В списке доступных компонентов раскройте Периферия, затем Отладка и Исполнение, и кликните Периферия идентификатора системы. 2. Кликните Добавить. Раскроется интерфейс MegaWizard для периферии идентификатора системы. На рисунке 5.10 показан графический интерфейс. Периферия идентификатора системы не имеет конфигурируемых пользователем настроек. Рисунок 5.10 – Окно для настройки модуля периферии индикатора системы 3. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а модуль периферии идентификатора системы сразу появится в таблице доступных компонентов. 4. Правым кликом на периферии идентификатора системы выберите Переименовать. 5. Введите имя sysid и нажмите Ввод. Добавление PIO Сигналы PIO – это простой способ для процессорной системы Nios II принимать входные и выводить выходные сигналы. Комплексные контрольные приложения могут использовать сотни сигналов PIO, которые может наблюдать процессор Nios II. В этом примере проекта используется восемь сигналов PIO, ведущих на светодиоды на плате. Выполните следующие пункты для добавления PIO. Выполните эти пункты даже, если на вашей плате нет светодиодов: 1. В списке доступных компонентов раскройте Периферия, затем Периферия микроконтроллера, и кликните PIO (Параллельные I/O). 2. Кликните Добавить. Раскроется интерфейс MegaWizard для PIO (Параллельных I/O). На рисунке 5.11 показан графический интерфейс. 3. Не меняйте настройки по умолчанию. Интерфейс MegaWizard устанавливает по умолчанию 8-ми битные выходы PIO, что полностью соответствует потребностям примера проекта. Рисунок 5.11 – Настройка портов ввода-вывода 4. Кликните Финиш. Вы вернѐтесь на вкладку Содержимое системы SOPC Builder, а модуль PIO сразу появится в таблице доступных компонентов. 5. Правым кликом на PIO выберите Переименовать. 6. Введите имя led_pio и нажмите Ввод. Определение базового адреса и приоритета запроса прерываний (IRQ) К этому моменту, вы добавили все необходимые аппаратные компоненты в систему. Теперь вам нужно определить, форму взаимодействия этих компонентов в системе. В этой секции вы назначите базовый адрес для каждого ведомого компонента, а также назначите приоритет запроса прерываний (IRQ) для JTAG UART и интервального таймера. SOPC Builder позволяет легко назначить базовые адреса с помощью команды Авто назначение базовых адресов. Для большинства систем, включая этот проект, допускается использование команды Авто назначение базовых адресов. Однако, вы, по необходимости, можете скорректировать базовые адреса. Следуйте следующим указаниям для назначения базовых адресов: ■ Ядра процессора Nios II имеют диапазон адреса в 31 бит. Вы можете назначить базовый адрес между 0x00000000 и 0x7FFFFFFF. ■ Программы для Nios II используют символьные константы для обращения к адресу. Не беспокойтесь о выборе значения адреса, потому что его просто запомнить. ■ Значения адреса разных компонентов, различающихся только одним битом адреса, способствуют созданию более эффективных устройств. Но не пытайтесь укомплектовать все базовые адреса в наименьший диапазон адресов, поскольку это уменьшает эффективность устройств. ■ SOPC Builder не пытается выстроить по порядку различные компоненты памяти в непрерывном поле адреса. Например, если вы хотите создать непрерывное поле адреса для внутри чиповой RAM и внешней RAM, вы должны однозначно задать базовые адреса. SOPC Builder имеет команду Авто назначение IRQ, которая позволяет подключить IRQ сигналы для получения правильных аппаратных данных. Однако, эффективное назначение IRQ требует понимание того, как программа обращается к ним. Поскольку SOPC Builder не управляет поведением программы, он не сможет предположить грамотное назначение IRQ. Nios II HAL интерпретирует малые значения IRQ наивысшим приоритетом. Компонент таймера должен иметь наивысший приоритет, чтобы правильно создавать системные такты. Для назначения нужных базовых адресов и IRQ, выполните следующие пункты: 1. В меню Система кликните Авто назначение базовых адресов, чтобы позволить SOPC Builder назначить функциональные базовые адреса каждому компоненту системы. Базовое и Конечное значения в таблице активных компонентов может меняться в зависимости от адресов, переназначаемых SOPC Builder. 2. Кликните на значение IRQ для компонента jtag_uart и выберите его. 3. Введите 16 и нажмите Ввод для назначения нового значения IRQ. На рисунке 5.12 показано состояние вкладки Содержимое системы в SOPC Builder для законченной системы. Рисунок 5.12- Вид готовой системы в SOPC Builder Генерирование системы SOPC Builder Сейчас всѐ готово для генерирования системы SOPC Builder. Выполните следующие пункты: 1. Кликните на вкладку Генерация системы. 2. Выключите Симуляция. Создание файлов симулятора проекта., чтобы сэкономить время, поскольку этот учебный курс не рассчинан на симуляцию аппаратной части. 3. Кликните Генерировать. Появится диалоговое окно Сохранить изменения, запрашивающее сохранение вашего проекта. 4. Кликните Сохранить. Начнѐтся процесс генерации системы. Процесс генерации может занять несколько минут. Когда он закончится, на вкладке Генерация системы отобразится сообщение: "Информация: Система сгенерирована успешно." На рисунке 5.13 показана успешная генерация системы. Рисунок 5.13 – Генерация системы 5. Кликните Выход для возвращения в программу Quartus II. Внедрение модуля системы SOPC Builder в проект Quartus II. Результатом работы SOPC Builder является модуль проекта, называемый системным модулем. Пример учебного проекта использует метод представления модуля проекта в виде блок-схемы, чтобы вы могли внедрить символ модуля вашего проекта first_nios2_system в виде .bdf файла. Внедрение модуля проекта зависит от метода разработки всего проекта Quartus II. Например, если вы использовали для разработки проекта Verilog HDL, вы можете внедрить модуль first_nios2_system, определѐнный в файле first_nios2_system.v. Чтобы внедрить модуль .bdf, выполните следующие пункты: 1. Дважды кликните в пустом месте между входными и выходными выводами. Раскроется диалоговое окно Символ. 2. Под Библиотеками, раскройте Проект. 3. Кликните на first_nios2_system. Диалоговое окно Символ показывает символ first_nios2_system. 4. Кликните ОК. Вы вернѐтесь в схему .bdf. Символ first_nios2_system перемещается с указателем мыши. 5. Разместите символ так, чтобы входы символа могли быть соединѐнными с шинами на левой стороне схемы. 6. Кликните на левую клавишу мыши, чтобы оставить символ в выбранном месте. 7. Если на вашей плате есть светодиоды, которыми может управлять Nios II, кликните и перетащите LEDG[7..0] и подключите их к порту out_port_from_the_led_pio[7..0 на символе first_nios2_system. Этим вы подключите выходные выводы LEDG[7..0] к системе first_nios2_system. На рисунке 5.14 показан файл схемы проекта, использующий выводы под светодиоды. Рисунок 5.14 – Файл схемы проекта 8. Если на вашей плате нет светодиодов, вы должны удалить выводы LEDG[7..0]. Для удаления выводов сделайте следующее: a. Кликните на выходной символ LEDG[7..0] для выбора его. b. Нажмите Удалить на клавиатуре. c. Для сохранения завершѐнного .bdf файла, кликните Сохранить в меню Файл.