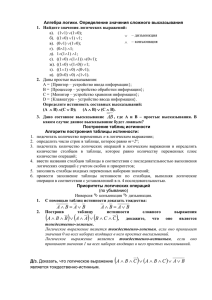

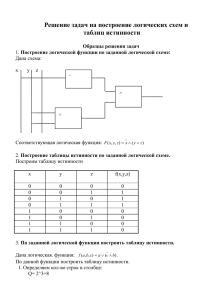

Министерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ (ТУСУР) Кафедра автоматизированной обработки информации (АОИ) ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ И УЗЛЫ лабораторная работа №3 по дисциплине Организация ЭВМ и систем д. т. н., профессор каф. АОИ ________ Замятин Н. В. «___»________2017 Оглавление Введение 3 1 Базовые логические элементы 1.1 Схема «И» 1.2 Схема «ИЛИ» 4 4 4 2 Триггер 2.1 Асинхронный RS-триггер 5 5 Томск 2017 2 2.2 Синхронный RS-триггер 2.3 D-триггер. 6 8 3 Регистр 3.1 Параллельные регистры 3.2 Последовательные регистры 8 9 9 4 Полусумматор 12 5 Сумматор 13 6 Шифратор 14 7 Дешифратор 15 8 Счетчик 16 10 Заключение 19 3 Введение Целью данной лабораторной работы является изучение видов логических устройств, цифровых схем, а также их синтез с помощью программы для моделирования электрических схем Electronics Workbench. 4 1 Базовые логические элементы Логический элемент компьютера — это часть электронной логической схемы, которая реализует элементарную логическую функцию. 1.1 Схема «И» Схема «И» реализует конъюнкцию двух или более логических значений. Таблица истинности схемы представлена в таблице 1.1. Таблица 1.1 – Таблица истинности схемы «И» X0 X1 Y 0 0 0 0 1 0 1 0 0 1 1 1 𝑌=𝑋 0⋅𝑋 1 Схема элемента «И» представлена на рисунке 1.1. Рисунок 1.1 – Схема «И» 1.2 Схема «ИЛИ» Схема «ИЛИ» реализует дизъюнкцию (логическое сложение) двух или более логических значений. Таблица истинности представлена в таблице 1.2. Таблица 1.2 – Таблица истинности схемы «ИЛИ» X0 0 0 1 1 X1 0 1 0 1 Y 0 1 1 1 𝑌 = 𝑋 0+𝑋 1 Схема элемента «ИЛИ» представлена на рисунке 1.2. Рисунок 1.2 – Схема «ИЛИ» 5 2 Триггер Триггеры – устройства с двумя состояниями, предназначенные для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти. 2.1 Асинхронный RS-триггер Асинхронный RS-триггер сохраняет своё предыдущее состояние при неактивном состоянии обоих входов и изменяет своё состояние при подаче на один из его входов активного уровня. При подаче активного уровня на вход S выходное состояние становится равным логической единице, а при подаче активного уровня на вход R выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы активные уровни не определено и зависит от реализации. Например, в триггере на элементах «или-не» оба выхода переходят в состояние логической единицы, которое сохраняется, пока на входах удерживаются логические нули. Таблица истинности асинхронного RS-триггера представлена таблицей 2.1. Таблица 2.1 – Таблица истинности асинхронного RS-триггера № S R Q(t) Q(t+1) 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 7 1 1 1 Запишем совершенную дизъюнктивную нормальную форму для Q(t+1): Q(t+1)=𝑆 × 𝑆 × 𝑆 + 𝑆 × 𝑆 × 𝑆 + 𝑆 × 𝑆 × 𝑆 Для выполнения минимизации построим карту Карно для асинхронного RS-триггера: 6 После минимизации получим функцию Q(t+1)=𝑆 × 𝑆 + 𝑆. Q(t+1)=𝑆 × 𝑆 + 𝑆=𝑆 × 𝑆 × 𝑆. Схема асинхронного RS-триггера представлена на рисунке 2.1. Рисунок 2.1 – Асинхронный RS-триггер 2.2 Синхронный RS-триггер Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс, то запоминать состояния логической схемы нужно только в определенные моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Таблица истинности синхронного RS-триггера представлена в таблице 2.2. 7 Таблица 2.2 – Таблица истинности 2синхронного RS-триггера C R S Q(t) Q(t+1) 0 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 1 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 Запишем совершенную дизъюнктивную нормальную форму для Q(t+1): Q(t+1)=С × 𝑆 × 𝑆 × 𝑆 + С × 𝑆 × 𝑆 × 𝑆 + 𝑆 × 𝑆 × 𝑆 × 𝑆 + 𝑆 × 𝑆 × 𝑆 × 𝑆+𝑆×𝑆×𝑆×𝑆+𝑆×𝑆×𝑆×𝑆+𝑆×𝑆×𝑆×𝑆 Для выполнения минимизации построим карту Карно для синхронного RS-триггера: После минимизации получим функцию Q(t+1)=𝑆 × 𝑆(𝑆) + 𝑆 × 𝑆. Q(t+1)=𝑆 × 𝑆(𝑆) + 𝑆 × 𝑆=𝑆 × 𝑆(𝑆) × 𝑆 × 𝑆. Схема синхронного RS-триггера представлена на рисунке 2.2. 8 Рисунок 2.2 – Синхронный RS-триггер 2.3 D-триггер. D-триггер имеет один информационный вход (D-вход). Бывают только синхронные D-триггеры. Состояние информационного входа передаётся на выход под действием синхроимпульса (вход С). Таблица истинности D-триггера представлена в таблице 2.3. Таблица 2.3 – Таблица истинности D-триггера C D Q(t) Q(t+1) 0 0 0 0 1 1 1 0 0 1 1 1 Булева функция примет вид: Q(t+1) = 𝑆 × 𝑆 + 𝑆 × 𝑆 = 𝑆 × 𝑆 + 𝑆 × 𝑆. Схема D-триггера представлена на рисунке 2.3. Рисунок 2.3 – D-триггер 3 Регистр Регистром называется устройство, используемое для хранения nразрядных двоичных данных и выполнения преобразований над ними. Регистр представляет собой упорядоченный набор триггеров,число n которых 9 соответствует числу разрядов в слове. По способу ввода-вывода информации регистры делятся на последовательные и параллельные. В 3.1 Параллельные регистры параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для разрядов обычно являются цепи тактирования, сброса/установки, разрешения выхода или приема, то есть цепи управления. Рисунок 3.1 - Параллельный регистр с RS-триггерами 3.2 Последовательные регистры Последовательные (сдвигающие) регистры представляют собой цепочку разрядных схем, связанных цепями переноса. Основной режим работы — сдвиг разрядов кода от одного триггера к другому на каждый импульс тактового сигнала. Специальный управляющий сигнал SL/R, задающий сдвиг регистра либо влево, либо вправо. Значения подаваемые на входы D каждого из триггеров при переходе от текущего состояния в следующее состояние. В таблице 3.1 отображены текущее и следующее состояние каждого из триггеров последовательного регистра. Таблица 3.1 - таблица истинности реверсивного сдвигающего регистра. 10 SL/R 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 t t+1 𝑄2 𝑄1 𝑄0 𝑄2 𝑄1 𝑄0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 𝐷2 𝐷1 𝐷0 0 0 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 1 HYPER LINK "http:// www.k m.ru/ref erats/E D86FD 9B0E76 4CB9A 052962 1772A D1FF" 11 D 1 D 2 = SL/R ⋅ Q 1 = SL/R ⋅ Q 0 + SL/R ⋅ Q D 0 = SL/R ⋅ Q 1 2 По полученным логическим выражениям синтезируем схему регистра. На основе полученных логических выражений и синтезированной схемы можно получить логическое выражение и схему для i-го триггера. D i = SL/R ⋅ Q i−1 + SL/R ⋅ Q i+1 Рисунок 3.2 - Схема последовательного регистра 12 4 Полусумматор Одноразрядный сумматор суммирует биты соответствующих разрядов двух двоичных чисел и реализует перенос в следующий разряд. Таблица истинности для полусумматора представлена в таблице 4.1. Таблица 4.1 – Таблица истинности полусумматора A B S P 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 Булевы функции примут вид: S =A × B + A × B = A × B × A × B, P = A × B. Схема полусумматора представлена на рисунке 4.1. Рисунок 4.1 - Полусумматор 13 5 Сумматор Сумматор состоит из нескольких сумматоров и учитывает единицы переноса разрядов, полученные от каждого полусумматора. Таким образом реализуется сложение многоразрядных чисел. Таблица истинности для сумматора представлена в таблице 5.1. Таблица 5.1 – Таблица истинности сумматора A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 S 0 1 1 0 1 0 0 1 P 0 0 0 1 0 1 1 1 P = A × B × C × A × B × C × A × B × C × A × B × C, S = A × B × C × A × B × C × A × B × C × A × B × C. Схема сумматора представлена на рисунке 5.1. Рисунок 5.1 - Сумматор 14 6 Шифратор Шифратор – комбинационная схема с несколькими входами и выходами, преобразующая сигнал, подаваемый на входы, в код на одном из выходов. Таблица истинности шифратора представлена в таблице 6.1. Таблица 6.1 – Таблица истинности шифратора Входы A B C D E 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Y0 =E + F + G + H, F 0 0 0 0 0 1 0 0 G 0 0 0 0 0 0 1 0 H 0 0 0 0 0 0 0 1 Y0 0 0 0 0 1 1 1 1 Выходы Y1 Y2 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 Y1 = C + D + G + H, Y2= B + D + F + H. Полученная булева функция имеет вид f = 𝑌 0 ×Y Y0 × Y1 × Y2 . Схема шифратора представлена на рисунке 6.1. Рисунок 6.1 –Схема шифратора на элементах ИЛИ 1 ×Y 2= 15 7 Дешифратор Дешифратор – комбинационная схема с несколькими входами и выходами, преобразующая код, подаваемый на входы, в сигнал на одном из выходов. Дешифратор с n входами имеет 2n выходов, каждому из которых соответствует единичный сигнал на одном выходе при нулях на всех остальных выходах.Таблица истинности дешифратора представлена в таблице 7.1. Таблица 7.1 – Таблица истинности дешифратора A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 С 0 1 0 1 0 1 0 1 Y0 1 0 0 0 0 0 0 0 Y1 0 1 0 0 0 0 0 0 Y2 0 0 1 0 0 0 0 0 Y3 0 0 0 1 0 0 0 0 Y4 0 0 0 0 1 0 0 0 Y5 0 0 0 0 0 1 0 0 Y6 0 0 0 0 0 0 1 0 Y0=A × B × С, Y1=A × B × С, Y2=A × B × C, Y3=A × B × C, Y4 =A × B × С, Y5=A × B × C, Y6 =A × B × С, Y7 =A × B × C. Схема дешифратора представлена на рисунке 7.1. Рисунок 7.1 – Дешифратор Y7 0 0 0 0 0 0 0 1 16 8 Счетчик Счетчик предназначен для подсчета числа входных сигналов. Таблица истинности счетчика представлена в таблице 8.1. Таблица 8.1 – Таблица истинности счетчика Q2(t) Q1(t) Q0(t) Q2(t+ Q1(t+ 1) 1) 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 1 0 1 0 1 1 1 1 1 0 1 1 1 1 1 0 0 Булевы функции примут вид: Q0(t+ 1) 1 0 1 0 1 0 1 0 D0 = Q 0 , D1 = Q 0 × Q1 × Q 0 × Q1 , D2 = Q 0 × Q1 × Q 2 × Q1 × Q 2 × Q0 × Q 2 . Схема счетчика представлена на рисунке 8.1. Рисунок 8.1 - Счетчик D2 D1 D0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 17 9. Заключение В ходе данной лабораторной работы были синтезированы логические схемы различных логических элементов и логических узлов. Работоспособность каждой схемы была проверена моделированием в программе Electronics Workbench.