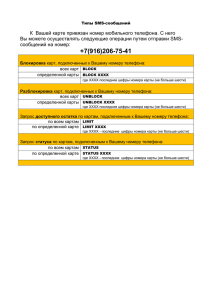

Микропроцессор 1804 от GhostAngeL | skachatreferat.ru Санкт-Петербургский государственный политехнический университет Факультет технической кибернетики Кафедра компьютерных систем и программных технологий Отчет по лабораторной работе (Учебная дисциплина «Организация ЭВМ и систем») Исследование секционного микропроцессора с микропрограммным управлением, с естественной, принудительной и стековой адресацией микрокоманд Работу выполнила студентка группы 3081/3 Р. Ю.А. Работу принял преподаватель ______________ П. Е.Г. подпись Санкт-Петербург 2012 Цель исследования: Целью данной лабораторной работы является практическое ознакомление с основными модулями микропроцессорного комплекта серии К1804, организацией и методикой построения микропроцессорных устройств на его основе, приобретение навыков программирования микропроцессоров данного класса. 1. 2. 3. 4. 5. Программа исследования: Изучить список микрокоманд ЦПЭ К1804ВС1 и методики его программирования. Рассмотреть принципы построения БМУ на основе БИС К1804ВУ1 и К1804ВУ3. Изучить режимы работы МП К1804 и приобрести начальные навыки программирования и построения простейших контроллеров на МП серии К1804 с помощью восьми тестовых микропрограмм. Написать программу преобразования 8-разрядного числа из кода Грея в двоичный. Написать программу умножения «старшими разрядами вперед» двух 4-разрядных чисел. Структурные схемы и краткое описание работы МП и исследуемой микропроцессорной системы: Центральный процессорный элемент (ЦПЭ) К1804ВС1 предназначен для арифметико-логической обработки данных и временного хранения операндов и результатов вычислений во внутренней регистровой памяти. Секционная структура ЦПЭ позволяет путем объединения нескольких секций строить операционные блоки процессоров с разрядностью, кратной четырем. Структурная схемасекции ЦПЭ (Рис. 1) содержит четыре основных блока: блок АЛУ, блок внутренней памяти, блок регистра Q и блок управления. Рис.1. Структурная схема четырёхразрядной микропроцессорной секции ЦПЭ К1804ВС1. Краткая характеристика блоков ЦПЭ: 1. Блок АЛУ выполняет простейшие арифметические (сложение и вычитание) и поразрядные логические операции (И, ИЛИ, отрицание с умножением, сложение по модулю два, проверку на эквивалентность) и формирует четыре признака результата: перенос из старшего разряда C4, переполнение OVR, знак результата F3 и признак нулевого результата Z. 2. Блок внутренней памяти состоит из регистрового ЗУ (РЗУ) емкостью 16 4-разрядных РОН, регистра-сдвигателя (Сд Д) на входе регистрового ЗУ, двух 4-разрядных буферных регистров (РА и РВ). Регистр-сдвигатель имеет дополнительные выходы (PR3, PR0) для организации сдвигов совместно с регистром Q и объединения с аналогичными регистрами других ЦПЭ. 3. Блок регистра Q состоит из дополнительного 4-разрядного регистра Q (РQ) и отдельного сдвигателя (Сд Q). Регистр Q позволяет выполнять сдвиговые операции над 8-разрядным словом, старшая часть которого задается регистром B, а младшая хранится в Q, также он используется в качестве приемника результата операции АЛУ или для сдвигов в нем параллельно над четырехразрядными данными, без учета переносов. 4. Блок управления формирует сигналы управления работой секции ЦПЭ. Является микропрограммным и также позволяет увеличивать адресное пространство памяти путем соединения нескольких секций управления адресом микрокоманды (СУАМ) друг с другом. Краткая характеристика СУАМ (К1804ВУ1): СУАМ предназначены для формирования адреса следующей микрокоманды. Источником адреса микрокоманд могут быть: счетчик микрокоманд, аппаратный стек, входящие в состав СУАМ, адресная частьрегистра микрокоманд, а также преобразователь начального адреса команд и векторов прерываний. Конкретный выбор осуществляется мультиплексором управляемым сигналами S0, S1, поступающими с контроллера последовательности микрокоманд K1804. Так же в СУАМ имеются: сигнал маскирования адреса ZA, сигналы PUP и FE управления работой стека и C0 управления счетчиком микрокоманд. Их генерирует на основе 4-разярдного поля перехода микрокоманды формирователь сигналов управления – К1804. Счетчик микрокоманд состоит из регистра счетчика МК и инкрементатора. Управляющий сигнал переноса C0 позволяет создать цикличность выполнения определенной команды (С0=0), если С0=1, то происходит увеличение адреса на выходе счетчика. Аппаратный стек на 4 уровня растет в сторону младших адресов и служит главным образом для организации возврата из подпрограмм. Он управляется сигналами PE (разрешения работы стека) и PUP (управление загрузкой/выгрузкой). Регистр адреса служит буфером для хранения адреса, поступающего на входы R3..R0 от внешнего источника. Разрешение записи осуществляется сигналом RE=0. Другим набором входов для связи с внешним источником является D3..D0. Рис. 2.Структурная схема СУАМ ( К1804ВУ1) Общая структурная схема всей микропроцессорной системы выглядит следующим образом: Рис. 3. Функциональная схема микропроцессорной системы Выполнение тестовых микропрограмм: Микропрограмма 1 иллюстрирует методы загрузки данных в РОН ЦПЭ. Текст микропрограммы приведен в таблице 1. Таблица 1 Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Адрес 000 001 002 003 004 005 «ДАННЫЕ» 0010 0010 0100 0100 0101 0101 С помощью указанных микрокоманд убедились, что можно загрузить любой изшестнадцати РОН произвольным числом меняя только содержимое полей В и D. Микрокоманда с адресом 005 в этой микропрограмме, передающая управление самой себе, является микрокомандой «останова». С помощью индикатора «ДАННЫЕ» убеждаемся, что микропрограмма «зацикливается» на микрокоманде с адресом 005, при этом любое последующее нажатие кнопки ПУСК не изменяет содержимое счетчика микрокоманд БИС К1804ВУ1. Загрузка Q выполняется аналогичными командами, однако для этого необходимо изменить приёмник результата. Текст микрооперации представлен в таблице 2. Таблица 2 Микропрограмма 2 иллюстрирует выполнение сдвиговых операций операндов 4-разрядной и 8-разрядной длины. Текст микропрограммы приведен в таблице 3. Таблица 3 Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: В результате выполнения команды по адресу 000 в РОН0 загружается число 0010 после чего происходит переход на следующий адрес. В процессе работы программы в командах сдвига осуществляется переход на адрес вектора, задаваемый клавишным переключателем АДРЕС, что позволяет производить сдвиг РОН необходимое число раз. Необходимо учитывать, что с появлением тактового импульса, сдвиг РОН происходит вне АЛУ, поэтому на выходной шине данных виден еще не сдвинутый РОН. При сдвиге РОН0 циклически влево его значение стало равно 0010. На клавишном регистре адреса установили код 002. При очередном нажатии кнопки ПУСК была считана и выполнена микрокоманда по второму адресу ЗУМК (сдвиг РОН0 циклически вправо). При первом нажатии кнопки ПУСК на индикаторе «ДАННЫЕ» появляется число не 0001, а 0100. При втором нажатии кнопки ПУСК на индикаторе «ДАННЫЕ» появляется число 1000. И только на третьем нажатии меняется направление сдвига (0100 наиндикаторе «ДАННЫЕ»). Пустая операция в конце программы не производит никаких модификаций значений регистров и ссылается сама на себя. Составим микропрограмму выполнения арифметического сдвига 8разрядной длины вправо и влево, а также 4-разрядного сдвига с вводом лог.0 в старшие (при сдвиге влево) или младшие (при сдвиге вправо) разряды РОН и регистра Q. Текст микропрограммы представлен в таблице 4. Таблица 4 Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Микропрограмма 3 иллюстрирует действие некоторых арифметических операций в ЦПЭ К1804ВС1. Текст микропрограммы приведен в таблице 5. Таблица 5 Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Адрес 000 001 001 002 002 003 003 004 005 006 007 008 «ДАННЫЕ» 0010 0011 0100 0011 0010 0101 1000 0011 0000 0101 0101 0110 009 009 0110 0110 Микрокоманды 000 и 001 используются для инкремента и декремента содержимого РОН0. Микрокоманды 002, 003 демонстрируют сложение (вычитание) содержимого РОН с константой. Микрокоманды 004, 005, 006 реализуют сложение содержимого двух РОН. Данная программа демонстрирует возможные арифметические операции с разным типом и числом операндов: РОН и D, РОН и РОН и т.д. В данную микропрограмму, как и в предыдущих пунктах, включены микрокоманды, в которых реализуется переход по адресу, формируемому клавишным регистром адреса, что позволяет выполнять арифметические операции, произвольное число раз. Микропрограмма 4 иллюстрирует работу БМУ при безусловных переходах. Текст микропрограммы приведен в таблице 6. Таблица 6 В процессе работы программы осуществляется безусловный переход к следующему адресу, либо переход,указанный в инструкции адреса. Последовательность адресов при выполнении программы: 000 -> 009 -> 010 -> 003 -> 004 -> 015 -> 000 -> ... Микропрограмма 5 иллюстрирует один из способов организации цикла с помощью стека. Текст микропрограммы приведен в таблице 7. Таблица 7 Данная микропрограмма иллюстрирует один из методов организации цикла с использованием аппаратного стека на четыре 4-разрядных слова (он же используется при реализации подпрограмм), в который можно записывать адреса микрокоманд, а затем осуществлять условный или безусловный переход по заданному адресу. В процессе работы микропрограммы осуществляется бесконечный цикл переходов по адресам: 000 -> 001 -> 002 -> 003 -> 010 -> 002 -> 003 -> … Микропрограмма 6 реализует обращение к подпрограмме и возврат из нее в соответствии с диаграммой переходов на рис.4. Рис. 4. Диаграмма переходов Текст микропрограммы представлен в таблице 8. Таблица 8 В микрокоманде 001 закодирована инструкция «Переход к подпрограмме» (код 0101 в поле 6 микрокоманды) и адрес первой микрокоманды подпрограммы (008 в поле 7), а в микрокоманде 010 указана инструкция «Возврат из подпрограммы» (код 0110 в поле 6). Последовательность адресов при выполнении программы: 000 -> 001 -> 008 -> 009 -> 010 -> 002 -> 003 -> 000 -> 001 -> 008 -> … Происходит обращение к подпрограмме и возврат из нее в соответствии с рисунком 4. Микропрограмма 7 иллюстрирует работу стека при вложении подпрограмм, когда одна подпрограмма вызывает другую, которая, в свою очередь, может вызвать третью и т.д. На рис. 5 предложена диаграмма организации последовательности выполнения вложенных микропрограмм. Рис. 5. Иллюстрация работы стека при вложении подпрограмм Текст микропрограммы приведен в таблице 9. Таблица 9 Последовательность адресоввыполняемых микрокоманд: 000 -> 001 -> 003 -> 006 -> 004 -> 007 -> 006 -> 008 -> 010 -> 006 -> 011 -> 013 -> 014 -> 012 -> 009 -> 005 -> 002 - > 000 - >… Происходит обращение к подпрограмме и возврат из нее в соответствии с рисунком 5. Ответы на вопросы: Какие ограничения на количество вложенных подпрограмм накладывает организация стека БИС СУАМ К1804 ВУ1? В БИС СУАМ К1804ВУ1 используется 4-х уровневый стек. Можно ли с использованием СУАМ К1804 ВУ1 реализовать микропрограмму, содержащую 10 подпрограмм? Да, если не превысить 4 уровня вложенности. Микропрограмма 8 иллюстрирует реализацию условных переходов в типовых микропрограммах. Текст микропрограммы приведен в таблице 10. Таблица 10 Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Адрес 000 001 002 003 001 002 003 001 002 255 «ДАННЫЕ» 1100 1101 1101 1101 1110 1110 1110 1111 1111 1111 Происходит инкрементирование R0.Условный переход будет сделан после сложения текущего R0=1111 c единицей, то есть произойдёт переполнение. Условные переходы в микропроцессоре К1804 реализуются по содержимому регистра состояния. В данной микропрограмме реализован УП по значению флага переноса. Следует отметить, что результаты в регистр состояния записываются после выполнения операции в момент появления тактового импульса, поэтому условный переход по этим результатам может быть сделан лишь в следующей команде. Составим и выполним микропрограмму определения значения выдвигаемого бита при сдвиге влево. Текст микропрограммы представлен в таблице 11. Таблица 11 При сдвиге влево анализируется значение старшего разряда, после этого выполняется сдвиг и проверка флага F3. Если F3=1, то выдвигаемый бит равен 1, в противномслучае – 0. Значение выдвигаемого бита записывается в регистр Q и выводится на индикатор «ДАННЫЕ». Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Составим и выполним микропрограмму определения значения выдвигаемого бита при сдвиге вправо. Текст микропрограммы представлен в таблице 12. Таблица 12 При сдвиге вправо исходное слово перед сдвигом маскируется словом маской 0001, содержащим 1 в младшем разряде слова. Затем выполняется сдвиг и реализуется условный переход по значению флага Z. Если Z=1, то выдвигаемый бит равен 0, в противном случае 1. Результат выдвигаемого бита записывается в регистр Q и выводится на индикаторы. Выполнили микропрограмму в пошаговом режиме, фиксируя результат выполнения отдельных микрокоманд по содержимому поля «ДАННЫЕ»: Адрес 000 001 002 003 004 005 007 008 «ДАННЫЕ» 0001 0001 0001 0000 0000 0001 0001 0001 Индивидуальное задание №1 Составить и выполнить программу преобразования 8-разрядного числа из кода Грея в двоичный код. Решение: Преобразование из двоичного представления числа в код Грея происходит по формуле: g n1 bn1 gi bi bi 1 , i 0, n 2 То есть для получения представления числа в коде Грея достаточно одной операции: bn1 g n1 bn2 bn1 g n2 ... ... ... b1 b2 g1 b0 b1 или b ⊕ (b ≫ 1). g0 Для обратного преобразования, воспользуемся элементарным свойством сложения по модулю два: x y y x С учетом того, что изначально от искомого числа нам известен только старший разряд, получим следующую последовательность действий: bn1 g n1 0 g n1 bn2 g n2 bn1 g n2 g n1 bn3 g n3 bn2 g n3 g n2 g n1 ... b0 g 0 b1 g 0 g1 ... g n1В зависимости от того, какую часть этих равенств использовать, получается две различных реализации алгоритма. Мы воспользуемся первой возможной реализацией. Решение заключается в следующем: часть bi = gi + bi-1 содержит цикл, на каждой итерации складывающий первоначальное число в коде Грея с результатом предыдущего вычисления, сдвинутым на один разряд вправо. При каждом выполнении тела цикла мы получаем новый разряд искомого числа. Так как старший разряд уже известен, число итераций равно n – 1, где n – разрядность данных. Представим алгоритм решения задачи в виде блок-схемы: Начало R0 ≔ D0 R1 ≔ D1 Q ≔ R0 R2 ≔ R1 R3 ≔ 7 R2 ≔ R2 ≫ 1 Q≔Q≫1 R2 ≔ R2 ⊥ 01112 R2 ≔ R1 ⊕ R2 Q ≔ Q ⊕ R0 R3 ≔ R3 - 1 да R3 != 0 Q≔Q R2 ≔ R2 Конец Текст программы представлен в таблице 13. Таблица 13 Адр ес ком анд ы Адр Тип ес пере пере хода хода 000 001 002 003 004 005 7 хххх хххх хххх хххх хххх хххх 006 007 хххх 0010 х011 х101 х100 хххх 0010 х011 х001 х110 0010 0010 0111 0001 0010 хххх 008 009 010 011 012 хххх хххх 005 хххх 011 0000 хххх хххх хххх хххх 6 0010 0010 0010 0010 0010 0010 0010 0010 0000 0010 0001 При емн ик резу льта та 5 х011 х011 х000 х011 х011 1100 х000 х011 х001 х000 х011 Микрокоманда Ист Функ А очн ция ик АЛУ опер андо в 4 3 2 х111 х011 хххх х111 х011 хххх х011 х011 хххх х100 х011 0001 х111 х011 хххх 1011 х011 хххх х000 х011 хххх х010 х011 х110 0001 хххх х011 х011 Выполняемая функция В D 1 0000 0001 0000 0010 0011 0010 0 D3..D0 D3..D0 хххх хххх 0111 хххх хххх 0011 хххх хххх 0010 хххх хххх хххх хххх хххх Загрузка в Р0 Загрузка в Р1 Q:=P0 P2:=P1 P3:=7 Арифм.сдвиг дв.слова вправоМаскир.стар.разр.нулем P2:=P2 P1 Q:=Q P0 P3:=P3 - 1 P3 != 0 Чтение Q (мл.тетр.) Чтение P2 (ст.тетр.) Операционный блок, установленный на стенде, ограничивает операнды АЛУ 4-разрядными числами. Чтобы оперировать 8-разрядным числом, использовался дополнительный регистр Q, где хранилась младшая тетрада числа. Для восьмиразрядного слова, образованного указанным в команде регистром и регистром Q, МП поддерживает операцию только арифметического сдвига вправо, поэтому в команде по адресу 006 производится коррекция, обнуляющая старший бит старшей тетрады полученного числа, маскированием регистра Р2 с 01112. В последней команде, отображающей старшую тетраду результата, содержащуюся в регистре Р2, используется безусловный переход на предыдущую инструкцию, отображающую младшую его часть. Это позволяет циклически выводить на ЖК-дисплей результат выполнения микропрограммы для удобного тестирования и отладки. Примеры вызова микропрограммы: Входные данные (в коде Грея) Результат (в двоичном коде) 1000 0000 1111 1111 1010 1010 1100 1100 0000 0010 0000 0011 1000 1001 1111 0001 Индивидуальное задание №2 Составить и выполнить программу умножения «старшими разрядами вперед» двух 4-разрядных чисел. Решение: Для решения задачи воспользуемся умножением старшими разрядами вперед со сдвигом множимого вправо и неподвижной суммы частичных произведений. Схема умножения показана на рис. 6. Особенностью данного способа умножения является необходимость использования регистра множимого и сумматора двойной длины по сравнению с длиной множителя. Рис. 6. Схема умножения Представим алгоритм решения задачи в виде блок-схемы: Начало R1:=D0 R2:=D1 R3:=R2 R4:=5 R4:=R4 - 1 да R4:=0 R1:=R1>>1 Q:=Q>>1 R6:=R6 R4:=R4 - 1 R5:=R5 R3:=R3