Содержание

Введение………………………………………………………

2

1.Система телеуправления и телесигнализаций…………. 3

1.1.Основные узлы телемеханических систем……………….. 3

1.2.Структурная схема передающего устройства…………….. 5

2.Кодирование сообщений…………………………………… 7

2.1.Двоичние и помехозащитные коды………………………. 7

3.Синтез специальных комбинационных схем………….. 10

3.1.Синтез шифратора………………………………………… 10

3.2.Преобразователь кодов……………………………………. 12

3.3. Мультиплексор……………………………………………. 15

3.4. Контрольный блок………………………………………… 17

4.Синтез схем конечных многоактных автоматов……… 19

4.1.Синтез генератора………………………………………… 19

4.2.Синтез счетчика…………………………………………… 25

5. Блок памяти………………………………………………… 30

6.Схема запуска и синхронизации………………………….. 33

Заключение…………………………………………………….. 35

Список использованныхлитератур…………………………… 36

1

Введение

Теория дискретных устройств является сравнительна молодой и

быстро развивающейся отраслей науки. Ее появление в 30-х годах XX

века связано с усложнением и совершенствованием релейных систем

управления, когда возникло необходимость в их математических

описаниях. Большое влияние на развитие теории дискретных устройств

оказало создание электронных вычислительных машин (ЭВМ).

Устройства железнодорожной автоматики и телемеханики в основном

относятся к классу дискретных. Отрасль науки и техники об

автоматически действующих устройствах и системах называется

автоматикой. Для выполнения тех же функций на больших расстояниях,

требующих для их преодоления специальных средств, применяют

устройства телемеханики. Телемеханика – отрасль науки и техники,

охватывающая теорию и технические средства контроля и управления

объектами и на расстоянии с применением специальных

преобразователей сигналов для эффективного использования каналов

связи.

Все системы автоматики и телемеханики, являются системами

переработки,

передачи,

воспроизведения,

хранения,

доставки

информации для управления некоторыми технологическими процессами.

В современных системах железнодорожной автоматики и

телемеханики для переработки информации используют дискретные

сигналы, в связи, с чем эти системы являются дискретными, особенно в

той части, которая связана с обработкой управляющей информации.

Задачей курсового проекта является разработка дискретного

передающего и приемного устройства системы телемеханики.

2

1. Система телеуправления и телесигнализации

1.1. Основные узлы телемеханических систем

Управление объектом и контроль его работы на больших расстояниях

требующих для их преодоления специальных средств осуществляются с

помощью устройств телемеханики.

В случае, когда расстояние между распорядительными и

исполнительными пунктами велико и в связи с этим возникает

необходимость уменьшить число каналов связи, применяют

телемеханический способ управления объектами. Для этого

передаваемый сигнал зашифровывают и посылают в линейную цепь в

закодированном виде, представляющим систему импульсов, обладающих

определенными признаками. На приемном пункте эти импульсы

воспринимают специальные устройства, которые расшифровывают и

приводят в действие управляемый объект или изменяют состояние

индикаторного прибора.

Каждая телемеханическая система состоит из отдельных узлов,

которые выполняют те или иные функции по передаче или приему кодов.

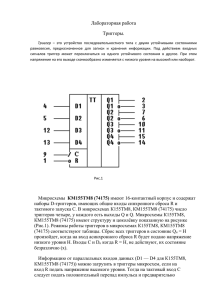

К функциональным узлам телемеханических систем (рис.1) относят

следующие узлы:

П – пусковой, служащий для восприятия сигналов пуска кодовых

устройств при переводе управляющих рукояток или изменении

положения объектов, образования шифраторных цепей, а также хранения

и обеспечения их передачи после освобождения линейной цепи;

Г – генератор импульсов, вырабатывающий импульсы тока,

используемые для передачи приказов;

Р – распределительный, преобразующий

последовательных импульсов тока и наоборот;

задания

в

серию

Ш – шифраторный, придающий импульсам кода определенные

признаки в соответствии с передаваемым приказом;

Л – линейный, предназначенный для восприятия импульсов кода;

Д – дешифраторный, осуществляющий дешифрирование принятого

кода и передачу воздействия исполнительным устройствам;

3

З – защитный, предназначенный для проверки правильности

генерирования кодов на передающей стороне и отсутствия искажения

приказов, зафиксированных на приемной стороне.

Рис.1.1. Структурная схема

телеуправления

Структурная схема приемного устройства состоит из следующих

блоков:

П – приемник, служащий для восприятия передаваемых сигналов;

ДМ – демультиплексор, предназначенный для осуществления

преобразования последовательных кодов в параллельные.

Б.П. – блок памяти, служащий для временного запоминания кодовых

комбинаций;

П.К. – преобразователь кодов, осуществляют преобразование

помехозащищенных кодов в двоичный;

ДШ – дешифратор, предназначенный для расшифровки двоичного

кода;

Г – генератор тактовых импульсов;

СЧ – счетчик, предназначенный для считывания импульсов и

управления работой демультиплексора;

З и О – схемы запуска и остановки устройства;

4

КБ – контрольный блок, служит для проверки переданного кода.

Структурная схема приемного устройства представлена на рис. 1.2.

510=1012

810=10002

1810=100102

2110=101012

3010=111102

1410=11102

5

2.Равновесный код

В этом коде к исходной n-разрядной комбинации добавляется еще nразрядов по правилу: если в исходной комбинации содержится четное

числе единиц, то добавляемая комбинация повторяет исходную: а если в

исходной комбинации содержится нечетное числа единиц, то

добавляемые комбинация инвертируют (т.е. 1 заменяется 0, а 0 на 1).

Например, если исходная комбинация 1001, то вместо нее будет

передоватся комбинация 10011001; если исходная комбинация 1101, то

вместо нее будет передана 1101 0010.

Емкость кода Бауэра N=2n/2 . При приеме кодовых комбинаций

осуществляется сложение по mod 2 информационной части (исходной

комбинации) и контрольный (добавки). При отсутствии искажений

получает либо все 0 либо все 1. Кодовое расстояние кода Бауэра d2 и

зависит от длины исходной кодовой комбинации. Избыточность кода

большая (И=1).

O’nlikdagi son Ikkilikdagi son

2110

710

1110

1610

1710

2410

2810

3010

101012

1112

10112

100002

100012

110002

111002

111102

Besh razryadli

kod

10101

00111

01011

10000

10001

11000

11100

11110

6

Ravnovesniy kod

10101001

00111001

01011001

10000111

10001011

11000011

11100001

11110000

3. Синтез специальных комбинационных схем

3.1.Синтез дешифратора

Устройство, распознающее различные кодовые комбинации,

называют

дешифратором

(декодером)

(рис.3.1).

Сигналы

четырехэлементной комбинации подаются на входы дешифратора. В

зависимости от вида кодовой комбинации на входе сигнал логической 1

появится только на одном определенном выходе, а на всех других будет

сигнал логического 0.

Таким образом, каждой кодовой комбинации на входе соответствует

свой выход, и если учесть, что число возможных четырехэлементных

кодовых комбинаций 24, максимальное число выходов дешифратора

будет 16. Рассмотрим построение дешифратора для определения

десятичного номера числа, представленного в двоичном четырехэлементном коде. Соответствия между двоичными и десятичными

числами приведены по задание. Все значения выходных переменных

определяются следующими логическими выражениями:

Рис. 3.1. Условные обозначения дешифратора

Система логических выражений для дешифратора

𝑦1 = 𝑥1 𝑥̅2 𝑥3 𝑥̅4 𝑥5

𝑦2 = 𝑥̅1 𝑥̅2 𝑥3 𝑥4 𝑥5

𝑦3 = 𝑥̅1 𝑥2 𝑥̅3 𝑥4 𝑥5

𝑦4 = 𝑥1 𝑥̅2 𝑥̅3 𝑥̅4 𝑥̅5

𝑦5 = 𝑥1 𝑥̅2 𝑥̅3 𝑥̅4 𝑥5

𝑦6 = 𝑥1 𝑥2 𝑥̅3 𝑥̅4 𝑥̅5

𝑦7 = 𝑥1 𝑥2 𝑥3 𝑥̅4 𝑥̅5

𝑦8 = 𝑥1 𝑥2 𝑥3 𝑥4 𝑥̅5

Составляем таблицу истинности дешифратора (ТИ)

7

Таблиa 3.1.

№

O’nlikdagi

son

1

2110

1

0

1

0

1

0

0

0

0

0

0

0

1

2

710

0

0

1

1

1

0

0

0

0

0

0

1

0

3

1110

0

1

0

1

1

0

0

0

0

0

1

0

0

4

1610

1

0

0

0

0

0

0

0

0

1

0

0

0

5

1710

1

0

0

0

1

0

0

0

1

0

0

0

0

6

2410

1

1

0

0

0

0

0

1

0

0

0

0

0

7

2810

1

1

1

0

0

0

1

0

0

0

0

0

0

8

3010

1

1

1

1

0

1

0

0

0

0

0

0

0

X1 X2 X3 X4 X5 Y8 Y7 Y6 Y5 Y4 Y3 Y2 Y1

Рис.3.2. Структурная схема дешифратора

8

3.2. Преобразователь кодов

Преобразователь – это устройство, преобразующее один код в другой.

В приемном устройстве он преобразует помехозащищенный код в

двоичный, а в передающем устройстве преобразователь кодов

преобразует двоичный код в помехозащитный. На рисунке -5

представлено условное обозначение преобразователя кодов.

Рис.3 Условное обозначение

преобразователя кодов.

Составляем таблицу истинности преобразователя кодов (ТИ)

Таблицa 3.1

O’nlikdagi

Himoya kod

son

№

𝑁10

𝑌1 𝑌2 𝑌3 𝑌4 𝑌5 𝑌6 𝑌7 𝑌8

1

1

2110

2

0

710

3

0

1110

4

1

1610

5

1

1710

6

1

2410

7

2810

1

8

3010

1

𝑄1 = 𝑦1 𝑦̅2 𝑦3 𝑦̅4 𝑦5 𝑦̅6 𝑦̅7 𝑦8

0

0

1

0

0

1

1

1

0

0

0

0

0

1

1

0

0

0

1

1

1

0

1

0

1 1 0 0

1 1 1 0

0

0

0

1

0

0

0

0

𝑄2 = 𝑦̅1 𝑦̅2 𝑦3 𝑦4 𝑦5 𝑦̅6 𝑦̅7 𝑦8

𝑄3 = 𝑦̅1 𝑦2 𝑦3 𝑦4 𝑦5 𝑦̅6 𝑦̅7 𝑦8

𝑄4 = 𝑦1 𝑦̅2 𝑦̅3 𝑦̅4 𝑦̅5 𝑦6 𝑦7 𝑦8

𝑄5 = 𝑦1 𝑦̅2 𝑦̅3 𝑦̅4 𝑦5 𝑦̅6 𝑦7 𝑦8

𝑄6 = 𝑦1 𝑦2 𝑦̅3 𝑦̅4 𝑦̅5 𝑦̅6 𝑦7 𝑦8

𝑄7 = 𝑦1 𝑦2 𝑦3 𝑦̅4 𝑦̅5 𝑦̅6 𝑦̅7 𝑦8

𝑄8 = 𝑦1 𝑦2 𝑦3 𝑦4 𝑦̅5 𝑦̅6 𝑦̅7 𝑦̅8

9

0

0

0

1

1

1

0

0

1

1

1

1

1

1

1

0

Ikkilik kod

𝑋1

𝑋2

𝑋3

𝑋4

𝑋5

1

0

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

1

0

0

0

0

1

1

0

1

1

0

0

0

0

1

1

1

1

0

1

0

0

0

𝑋1 = 𝑄1 ∨ 𝑄4 ∨ 𝑄5 ∨ 𝑄6 ∨ 𝑄7 ∨ 𝑄8

𝑋2 = 𝑄3 ∨ 𝑄6 ∨ 𝑄7 ∨ 𝑄8

𝑋3 = 𝑄1 ∨ 𝑄2 ∨ 𝑄3 ∨ 𝑄7 ∨ 𝑄8

𝑋4 = 𝑄2 ∨ 𝑄3 ∨ 𝑄8

𝑋5 = 𝑄1 ∨ 𝑄2 ∨ 𝑄3 ∨ 𝑄5

Рис.3.2. Структурная схема преобразователь кодов

10

3.3. Думультиплексор

Демультиплексоры - эти устройства выполняют функции,

противоположные мультиплексорам. У демультиплексора один вход и

много выходов (рис. 14). Вход подключается к выходу, имеющему

заданный адрес.

Рис. 3.1. Условное обозначение демультиплексора

Рис. 3.2. Схема коммутации с несколькими входами и выходами

С использованием мультиплексоров и демультиплексоров можно

строить схемы коммутации с n направлений в m. В схеме, приведенной на

рис. 6, по заданным адресам любой из входов может быть подключен к

любому из выходов. Число выходов увеличивают каскадным включением

демультиплексоров. К каждому выходу демультиплексора первого

каскада может быть подключен демультиплексор второго каскада.

Демультиплексор может использоваться как дешифратор. В этом

случае на вход демультиплексора подается константа D=1, а на адресные

входы — принимаемая кодовая комбинация. В зависимости от значения

переменных на адресных входах логическая 1 будет лишь на одном из

выходов демультиплексора.

Пример: Составляем ТИ

переключательных функций.

и

11

по

ней

определяем

формулы

Рис.3.3. Структурная схема DMS

Таблицa 3.4.

A4 A3 A2 A1 Q10 Q9 Q8 Q7 Q6 Q5 Q4 Q3 Q2 Q1

0

0

0

0

0

0

0

0

D

0

0

0

0

0

0

0

0

D

0

0

0

0

0

0

0

0

0

D

0

0

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

D

D

0

0

0

0

0

0

0

1

1

0

1

1

0

0

0

0

0

0

0

0

D

D 0

0 0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

D

0

0 0

0

0

0

0

1

1

0

0

0

0

0

1

0

D

D

0

0

0

0

0

0 0

0 0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

0

0

0

12

Рис.3.6. Структурная схема демультиплексор.

13

4. Контрольный блок

Частота пути разработки специальных комбинационных схем

(шифраторов, сумматоров, преобразователей кодов и др) могут

возникнуть ошибки, что приведёт к дальнейшей передачи заранее

искажённой информации. Для избежание неправильностей при

проектирование устройств используется так называемая контрольная

блок. Задача этой схемы состоит в том, чтобы распознать и выдать

искажённый сигнал. На выходе контрольнойблок подключаем лампочку,

и если сигнал без помех, то лампочка горит, если же с помехами, то нет.

Примем условное обозначение контрольной блок, показанное на рисунке.

Рис.4.1. Условное обозначение

Контрольный блок

При подаче на входы контрольной схемы комбинации преобразователя

кода (т.к контрольная схема проверяет правильность работы шифратора

и преобразователя кодов) без искажений, на выходе должна появиться

ложная единица. Число входов контрольной схемы равно количеству

разрядов преобразователя кодов.

Таблицa 4.2.

№

𝑁10

𝑥1

𝑥2

𝑥3

𝑥4

𝑥5

𝑥6

𝑥7

𝑥8

𝑦

1

2110

1

0

1

0

1

0

0

1

1

2

710

0

0

1

1

1

0

0

1

1

3

1110

0

1

0

1

1

0

0

1

1

4

1610

1

0

0

0

0

1

1

1

1

5

1710

1

0

0

0

1

0

1

1

1

6

2410

1

1

0

0

0

0

1

1

1

7

2810

1

1

1

0

0

0

0

1

1

8

3010

1

1

1

1

0

0

0

0

1

14

Система логических выражений для Контрольный блок:

𝑦 = 𝑥1 𝑥̅2 𝑥3 𝑥̅4 𝑥5 𝑥̅6 𝑥̅7 𝑥8 ∨ 𝑥̅1 𝑥̅2 𝑥3 𝑥4 𝑥5 𝑥̅6 𝑥̅7 𝑥8 ∨ 𝑥̅1 𝑥2 𝑥̅3 𝑥4 𝑥5 𝑥̅6 𝑥̅7 𝑥8

∨ 𝑥1 𝑥̅2 𝑥̅3 𝑥̅4 𝑥̅5 𝑥6 𝑥7 𝑥8 ∨ 𝑥1 𝑥̅2 𝑥̅3 𝑥̅4 𝑥5 𝑥̅6 𝑥7 𝑥8 ∨ 𝑥1 𝑥2 𝑥̅3 𝑥̅4 𝑥̅5 𝑥̅6 𝑥7 𝑥8

∨ 𝑥1 𝑥2 𝑥3 𝑥̅4 𝑥̅5 𝑥̅6 𝑥̅7 𝑥8 ∨ 𝑥1 𝑥2 𝑥3 𝑥4 𝑥̅5 𝑥̅6 𝑥̅7 𝑥̅8

Рис.4.2

Структурная схема Контрольный блок

15

5. Синтез схем многотактных конеяных автоматов

5.1. Синтез генератора

Конечный автомат, т.е. автомат с конечным числом состояний, задается

шестью множествами:

( A, S ,V , s0 , (a, s), (a, s)) , где

a1 , a2 ,..., a N - входной алфавит

S s0 , s1 , s 2 ,..., s R - внутренний алфавит

V v1 , v2 ,..., vM

- выходной алфавит

- функция переходов;

состояние автомата.

( a, s )

( a, s )

- функция выходов; s0 – начальное

Рис.5.1. Абстрактная модель КА.

Функция переходов и выходов могут

графическим или аналитическим способам.

быть

заданы

табличным,

Для построение структурной схеме необходимо:

1.

Приписать каждой букве аi входного алфавита А, совокупность

значений сигналов х1, х2, . . ., хn (хi {0, 1}) физических входов. Это называется

кодированием входных сигналов.

16

2.

Приписать к каждой букве vi выходного алфавита V совокупность

значений физических выходов z1,z2,…,zm(zi=0,1) Этот этап называется

кодированием выходных сигналов.

3.

Определить количество и тип элементов памяти ЭП.

4.

Приписать каждому состоянию siзаданного абстрактного автомата,

совокупность состояний (значений) ЭП y1, y2, . . ., yr (yi {0, 1}).

5.

Найти переключательные функции, т.е. функции включения ЭП y1,

y2, . . ., yrи функции выходов z1,z2,…,zm, описывающие работу логических схем

и определяющие структуру комбинационной части автомата.

Генератор

предназначен

для

формирования

стабильной

последовательности импульсов прямоугольной формы. Количество

внутренних состояний генератора обозначается через М, например М2, М4 и

т.д. Пример: генератор тактовых импульсов должен выдавать

последовательность импульсов по М2, т.е. автомат имеет четыре состояние.

Зададим алгоритм функционирования КА с помощью графов в абстрактной

форме.

Данный абстрактный автомат

задан (представлен) на трех

множествах:

a1 , a2 ;

S s0 , s1 , s2 , s3

Рис.5.2. Граф переходов генератора

V 1 ,2 ;

Заданный граф переходов

генератора соответствует графу

автомата Мура у которого

выходные сигналы на данный

момент времени определяются

только внутренними состояниями

автомата.

По графу определим:

1. Количество физических входов ”n” автомата, необходимых для

представления N входных букв определяем из условия: N 2 n . Так как

N 2(a1 и a2 ), то n 1.

Выберем вариант кодирования входного сигнала Х в соответствии с

таблицей 5.

17

2. Количество физических выходов ”m” автомата необходимых для

представления М выходных букв, определяется из условия: М 2 m . Так как

M 2(v1 и v2 ), то достаточно иметь один выход m 1 .

Вариант кодирования выходов приведен в таблице 6.

3. Количество элементов памяти ”r”, необходимых для представления

Rвнутренних состояний, определяется из условия: R 2 r . Так как,

R 4(s0 , s1 , s2 , s3 ), то минимальное число элементов памяти будет r 2 .

Тип элементов памяти по заданию: RS – триггеры.

4. Выберем вариант кодирования

соответствии с таблицей 7.

А

Х

а1

0

а2

1

Таблица 7

V

внутренних

состояний

Z

S

v1

0

s0

0

0

v2

1

s1

0

1

s2

1

1

s3

1

0

Таблица 5

y1

КА

в

y2

Таблица 6

5. По графу автомата с учетом таблиц 1, 2, 3 строим каноническую таблицу

включения, которая определяет все возможные комбинации воздействий

входным сигналов на внутренние состояния КА. Здесь следует иметь в виду,

что в соответствии с таблицами 1, 2, 3 : Х={0, 1} – входной алфавит реального;

Z={0, 1} выходной алфавит реального КА; y={y1, y2} – внутренний алфавит

состояний реального КА.

Каноническая таблице включений (полная кодированная

переходов ТП) представлена на представлена на таблице 8.

18

таблица

Таблица 8.

X (t )

Y1 (t )

Y2 (t ) Y1 (t 1)

Y2 (t 1)

Z (t 1)

J1

K1

J2

K2

0

0

0

0

0

0

0

~

0

~

0

0

1

0

0

0

0

~

~

1

1

0

0

0

1

1

0

~

1

~

1

0

1

0

0

0

0

~

~

1

Первые три столбца X (t ), Y1 (t ), Y2 (t ) заполняются так, чтобы каждому

значению входного сигнала X (t ) соответствовали бы все значения внутренних

состояний на данный момент времени. Столбцы [ Y1 (t 1) , Y2 (t 1) ] заполняются в

зависимости от схемы графа с указанием закодированного значения состояний

КА на момент времени (t 1) . Например, при воздействии на S 0 (0,0) входной

буквы a1 (0) , автомат согласно графу переходов при (t 1) остается в прежнем

состоянии S 0 (0,0) и формирует ту же выходную букву 1 (0) . При воздействии

на S1 (0,1) входной буквы a1 (0) , автомат переходит в состояние S 0 (0,0) и

формирует выходную букву 1 (0) . При воздействии же на S 0 входного сигнала

a2 (1) автомат в следующий такт времени (t 1) переходит в состояние S1 (0,1) и

формирует выходной сигнал 2 (1) и т.д.

Состояние выхода Z (t 1) определяется также с учетом таблицы

кодирования выходных сигналов табл.6. Столбцы 7,8 и 9,10 заполняются в

соответствии с работой первого ( J1 , K1 ) и второго ( J 2 , K 2 ) триггера согласно

таблице 5 следующим образом:

Для первого триггера в момент времени t Y1 (t ) 0 , а в следующий момент

времени Y1 (t 1) 0 , то переход 0 0 для триггера JK соответствует значениям

сигналов на J ~ , на K – 0 и т.д.

19

6. По канонической

таблице 4 включения определяем СДНФ схем

функционирования автомата.

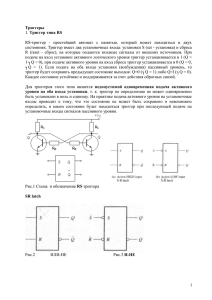

JK-триггер

Синхронный одноступенчатый JK-триггер, схема которого приведена на

рис. 10, имеет два информационных входа J и К и тактовый вход

синхронизации. Кроме того, триггер имеет асинхронные входы R и S, на

которые подаются входные сигналы при С = 0 с целью принудительной

установки триггера в нужное состояние. В этом случае во время управления

триггером, как синхронным устройством при С =

Q

J K

1, на асинхронные входы должны подаваться

t t+1

сигналы 1. В отличие от триггера RS –типа при

0→0

0

~ условии J=1 K=1 он осуществляет инверсию

предыдущего состояния (т.е. перебрасывается при

0→1

1

~

одновременном поступлении J=1 K=1). Однако

1→1

~

0 Одноступенчатые JK- триггеры при этом работают

нестабильно, входя в режим генерации, если

1→0

~

1

входной сигнал для асинхронных триггеров

больше по продолжительности, чем время

срабатывания JK-триггера, а в синхронном - если синхроимпульс по

продолжительности больше времени срабатывания триггера (что обычно и

бывает). По этой причине в сериях базисных элементов содержатся только

двухступенчатые JK-триггеры.

Схемы двухступенчатых триггеров универсального типа имеют повышенную

стабильность и помехоустойчивость работы. Триггеры имеют входы

несинхронизируемой установки R и S, с помощью которых, при отсутствии

синхроимпульса (С=0), триггер может быть установлен в состояние 1 путем

подачи S=1, либо в состояние 0 путем подачи R=1.

20

Рис. 5.3. Синхронный одноступенчатый JK-триггер

Для определения схемы включения первого триггера в форме СДНФ надо

объединить дизъюнкцией конституенты единицы тех наборов значений

X (t ), Y1 (t ), Y2 (t ) , для которых сначала вход R, а затем вход S принимают значение

1 (принимаем где нужно значение ~ за 1). Аналогично определяются функции

включения второго триггера, (значение ~ принимается за 1 в тех случаях, когда

данная операция позволяет минимизировать полученную СДНФ). При этом,

однако, следует иметь в виду, что для RS триггеров функции YR и YSне должны

одновременно быть равными 1.

Имеем триггеров:

K1 x y1 y 2 x y1 y 2 x y1 y 2 x y1 y 2

J 2 xy1 y 2 x y1 y 2 x y1 y 2

K 2 x y1 y 2 x y1 y 2 x y1 y 2

После минимизация

K 1 x y1 x y1

J 2 x y 2 x y1 y 2 K 2 x y1 y 2 x1 y1

21

Pис 5.4 Структурная схема генератора представлена.

5.2. Синтез счетчика

Каждый счетчик имеет конечное число состояний и может фиксировать

только определенное число N активных импульсов (сигналов). После

поступления на вход последнего N – ного сигнала счетчик возвращается в

исходное состояние, после чего начинается новый цикл его работы. Для

фиксации N сигналов счетчик должен иметь N внутренних состояний.

1). Число внутренних состояний в нашем N=10, так как количество

информационных выходов преобразователь кодов n=10 и счетчик должен

считать только до 10.

22

Рис.5.2.1.Граф переходов (диаграмма) переходов.

Рис.5.2.2. Кодированный граф

Количество элементов памяти (триггеров) определяем из условия: R 2 r и

10 2 4 и r 4 - число триггеров. Количество физических выходов, необходимых

для представления М выходных букв определяется из условия M 2 m 10 2 m и

m=3. Поскольку модель нашего счетчика удовлетворяет условию: 2 r 1 R 2 r и

2 3 10 2 4 , то для его построения требуется индивидуальное управление

каждым триггером.

D-триггер

В синхронных дискретных устройствах D-триггер реализует функцию

временной задержки и имеет только режимы установки в состояние 1 и 0. В

23

связи с этим асинхронный D-триггер (рис. 18) обычно не применяется, т.к. его

выход будет просто повторять входной сигнал.

Рис. 5.2.3. Асинхронный D-триггер

Синхронный триггер D – типа имеет информационный вход D и вход

синхронизации С (тактовый). Состояние триггера после прихода тактового

импульса (С=1) в момент времени (t+1) совпадает с уровнем входного сигнала

на входе D, действовавшего в момент времени t. В D триггере осуществляется

задержка входного сигнала на время паузы между синхроимпульсами

(задержка на полпериода). Для задержки на один такт используется

двухтактный D-триггер.

Условное обозначение (а) и структурная схема (б) синхронного

одноступенчатого D –триггера на элементах 2И-НЕ приведены на рис. 19.

а)

б)

Рис. 5.2.4. Синхронный D-триггер

Граф переходов нашего счетчика имеет вид (рис.20.)

Кодированный граф (диаграмма) переходов счетчика на трех триггерах

представлен на рис.6.4.

2) Составим далее кодированную таблицу переходов ТП, содержащую 2 r

клеток. Каждая клетка соответствует состоянию системы из r – триггеров. В

клетках, соответствующих состояниям не использованным для кодирования

диаграммы переходов проставляется знак неопределенности (~), а в остальных

клетках – коды тех состояний, в которые осуществляется переход по

диаграмме состояний из состояния, отвечающего данной клетке. Например, по

24

диаграмма состояний, из состояния АВС=110 идет переход в 000, а из

состояния АВСD=1001, переход в 100 и т.д., согласно диаграмме переходов.

В примере младшему разряду двоичного кода соответствует триггер С,

затем идут старшие – В и А.

Триггер С переключается всякий раз, когда сигнал на его входе изменяет

свое значение с 0 на 1, т.е. 0→1.

Триггер В изменяет свое состояние в моменты переключения триггера С из

состояния 1 в состоянию 0, т.е. 1→0. Аналогично работает триггер А в

зависимости от состояния триггера В.

Таблица 11

А

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

В

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

С

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

В исходном состоянии в счетчике

записано двоичное число 000 (все

триггеры

находятся

в

исходном

состоянии). При поступлении первого

активного сигнала («1») на вход

счетчика, переключается триггер С, что

соответствует записи 1 в младший

разряд. В дальнейшем при поступлении

каждого нового активного импульса

(«1») на вход счетчика, двоичное число

будет увеличиваться на 1 (табл.11.). При

поступлении последнего сигнала счетчик

возвращается в исходное состояние.

3) По таблице переходов 10. составляем карты Карно. Задающие функции

воздействия (включения) на входы D триггеров.

25

При составлении карт

Карно используем таблицу 12.

Определяющую

значение

входных сигналов D – триггера

при его переходе из одного

состояния в другое.

Таблица 12

Переход

Q(t) Q(t+1)

0

0

1

1

Вход

D

0

1

0

1

0

1

0

1

Карты Карно для триггеров АВСD.

Верхний левый элемент карты соответствует состоянию счетчика

АВС=000. По таблице переходов определяем, что из данного состояния

счетчик переходит в состояние АВС=100. Состояние триггера А изменяется с

0 на 1, т.е. 0→1. Этому изменению состояния триггера соответствует значение

входных сигналов D=1. Поэтому их записывают в верхний левый элемент

карты Карно триггера А. Состояние триггеров В и С меняются так: 0→0, т.е.

не изменяются, что соответствует D=0. Эти значения также записывают в

верхний левый элемент карт Карно для триггеров В и С. Аналогично

заполняют

СD

11

10

01

00

остальные

АВ

клетки.

0011

0010

0001

0000

00

4)

0111

0110

0101

0100

01

~

~

1001

1000

10

~

~

~

~

11

Минимизируем карту Карно по D входам. Для проведения минимизации:

1) Все единицы должны быть объединены прямоугольными контурами; 2)

во всех клетках контура должны быть «1»; 3) контуры могут накладываться

друг на друга; 4) число клеток в контуре кратно 2; 5) выбирать контуры с

наибольшим числом клеток.

По составленным контурам записываем аналитические выражения. Они

включают в себе те переменные, которые полностью перекрывают контура.

26

4) Минимизируем карту Карно по Dвходам. Для проведения минимизации

A

0

0

0

0

0

0

1

0

~

~

~

~

1

0

~

~

D

C

B

̅ 𝑉 𝐴𝐵𝐶𝐷 = 𝐴𝐵𝐷 𝑉 𝐵̅𝐶𝐷

̅

𝐷𝐴 = 𝐴𝐵𝐶𝐷 𝑉𝐴𝐵𝐶𝐷 𝑉 𝐴̅𝐵̅𝐶𝐷

Для триггера В:

A

0

0

1

0

1

1

0

1

~

~

~

~

0

0

~

~

C

27

B

D

𝐷𝑏 = 𝐴𝐵𝐶𝐷𝑉𝐴𝐵𝐶𝐷 𝑉𝐴B𝐶𝐷 𝑉𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉

𝑉 𝐴𝐵𝐶𝐷 = 𝐴𝐵𝐶𝐷 𝑉𝐴𝐶𝐷 𝑉𝐴𝐵𝐶𝐷 𝑉 𝐴𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷

Для триггера C:

A

0

1

0

1

0

1

0

1

~

~

~

~

0

0

~

~

D

C

B

𝐷𝑐 = 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 =

= 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶

Для триггера D:

A

1

0

0

1

1

0

0

1

~

~

~

~

1

0

~

~

D

C

B

𝐷𝑑 = 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉𝐴𝐵𝐶𝐷 𝑉𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 𝑉

𝑉 𝐴𝐵𝐶𝐷 𝑉 𝐴𝐵𝐶𝐷 = 𝐵𝐶𝐷 𝑉𝐵𝐶𝐷 𝑉 𝐵𝐶𝐷 𝑉 𝐵𝐶𝐷

28

1) Все единицы должны быть объединены прямоугольными контурами; 2) во всех

клетках контура должны быть «1»; 3) контуры могут накладываться друг на друга;

4) число клеток в контуре кратно 2; 5) выбирать контуры с наибольшим числом

клеток.

По составленным контурам записываем аналитические выражения. Они включают

в себе те переменные, которые полностью перекрывают контура.

Рис.20. Структурная схема счетчика

29

6. Блок памяти

Блок памяти включается между преобразователем кодов и

мультиплексором. Он предназначен дляудержание на некоторое время

сигналов поступающих от мультиплексора и затем одновременной выдачи их

на их вход преобразователя.

В качестве элементов памяти ЭП применяют триггеры. Триггер

представляет собой устройства двумя устойчивыми состояниями,

обозначаемыми через 1 и 0. Он удобен для обработки двоичной информации.

Двум устойчивым состояниям триггера соответствуют значения входных

сигналов логического 0 или 1.

Записанная в триггере информация сохраняется до тех пор пока не

измениться состояние триггере. Изменение информации производится

переводом триггера из одного устойчивого состояния в другое при помощи

входного сигнала.

RS –триггера

Схема асинхронного (несинхронизируемого) RS-триггера на элементах 2ИНЕ приведена на рис. 18.

Рис. 6.1. Асинхронный RS - триггер

30

Синхронный RS – триггер имеет дополнительный вход для

синхронизирующего (тактового) импульса (С – вход). Если сигнал на входе

С=0, то оба входных логических элемента В1 и В2 закрыты (на их выходах –

логические 1 и сигналы на входах S и R не оказывают никакого влияния на

состояние триггера). При С=1 состояние триггера определяется состоянием

входов S и R . Условное обозначение (а) и структурная схема (б)

одноступенчатого синхронного RS - триггера на элементах 2 И-НЕ приведены

на рис.19. Таблица истинности отражена в таблице 1.

Необходимо подчеркнуть, что для обеспечения правильной работы

синхронных триггеров информационные сигналы должны изменяться в

течение паузы между синхроимпульсами, т.е. при С=0. D-триггер является

одним из широко употребляемых триггеров.

a)

б)

Рис. 7.2. Условное обозначение и структурная схема синхронного RS –

триггера

Граф переходов нашего счетчика имеет вид (рис.20.)

Кодированный граф (диаграмма) переходов счетчика на трех триггерах

представлен на рис.17.

2) Составим далее кодированную таблицу переходов ТП, содержащую 2 r

клеток. Каждая клетка соответствует состоянию системы из r – триггеров. В

клетках, соответствующих состояниям не использованным для кодирования

диаграммы переходов проставляется знак неопределенности (~), а в остальных

клетках – коды тех состояний, в которые осуществляется переход по

диаграмме состояний из состояния, отвечающего данной клетке. Например, по

диаграмма состояний, из состояния АВС=110 идет переход в 000, а из

состояния АВС=011, переход в 100 и т.д., согласно диаграмме переходов.

31

Рис. 7.3. Структурная схема блока памят

32

6. Схема запуска и синхронизации

Схема запуска работает следующим образом: считаем, что генератор

приемного устройства работает синхронно и синфазно с генератором

передающего устройства. Какой бы сигнал не поступил с линии через элемент

И на вход R триггера RS всегда поступает 1. На вход S триггера подаем 0. В

результате на выходе Q триггера имеем 1.

В начальный момент времени счетчик в нуле. Генератор начинает подавать

импульсы. Сигналы от счетчика поступают на демультиплексор на его

адресные шины, которые производят коммутацию входе D демультиплексора

с соответствующими выходами.

После того как счетчик отсчитал 10 тактов и MS полностью отработал,

необходимо остановить генератор. Если посмотреть на граф счетчика, то

последнее седьмое состояние – это 1001. Следовательно необходимо

остановить работу генератора тогда, когда счетчик будет в состоянии 000. Для

этого со счетчика выводим на элемент ИЛИ-НЕ 3 шины. На выходе этого

элемента 1 будет лишь в единственном случае. Её (единицу) мы посылаем на

вход R триггера RS. В состоянии R=1, S=1 на входах триггера, он осуществляет

инверсию предыдущего состояния, т.е. переключается и на его выходе

появляется 0. В результате генератор прекращает работу и счетчик

останавливается.

Для сброса блока памяти (триггеров) в исходное состояние, т.е. обнулить

память, на входы R триггеров через дифференциальную цепочку подается

кратковременный импульс – «1».

Для подачи синхроимпульса во второй каскад блока памяти (если БП

двухкаскадный) используется последняя кодовая комбинация, выдаваемая

счетчиком (110), которая подается через ИЛИ на вход С триггеров. В

результате триггера второго каскада на время первого такта генератора,

переключаются (ИЛИ нет) в зависимости от состояний асинхронных триггеров

первого каскада, т.е. повторяют их состоянии и на преобразователь кодов ПК

подается параллельная кодовая комбинация помехозащитного кода,

поступившего с линии связи. Обнуление триггеров второго каскада

производится подачей 000 на входы С и R в следующем такте.

33

34

Заключение.

В данном курсавом проекте передающей устройство.

По

структурной схеме передающей устройство двоичное код с равновесный.

Полученной помехазашишунной код отражается преобразательямкодов.

Cтруктурной

схема

передающей

устройство

генератор

вырабативает кодовые импульса которых поступающие в счётчик.

После этого устройства мултиплексор преобразюшие паралельное

времени сигнала в последавательном. Далее сигналы поступаюшие блок

памяти сохраняються и передающие в преобразователь кодов.

После преобразователь кодов импульсов поступаюшие шифратор.

Mултиплексоры

эти

устройства

выполняют

функции

противоположные демултиплексором. Mултиплексор ( управляеми

коммутатор ) передназначнен для преобразованный паралельных во

времени импульсов в последовательные. Мултиплексор имеет две группи

входом:информатционние

входы;

адресние

входы.

Выходу

мултиплексора один частота разработки специальных комбинационных

схем ( шифратор, сумматор, преобразователей кодов и д.р.). Могут

вознипуть ошибки, что праведет и дольнейшей передачи заданним

искашенной информации. Для избежалие неправильностей при

проектрование устройств используйся так называимая контролная схем.

Кроме по мего добовлетель также другие устройства и приеминая схема

начинает работат.

35

Список использованных литературa

1. Сапожников В.В., Кравцов Ю.А., Сапожников Вл.В. Теория дискретных

устройств железнодорожной автоматики, телемеханики и связи. - М.: УМК

МПС, Россия 2001-учебник для ВУЗов ж.д. трансп.

2. Рахметов Г.Р., Хорунов Ш.Р., Махмудова Р.С. Мантикий элементларни

тадкик этиш ва чекли автоматлар схемаларнинг синтези. Методик кырсатма.

Ташкент, 1993й.

4. Рахметов Г.Р., Хорунов Ш.Р. Дискрет курилмалар назарияси маърузалар

матни. Тошкент, 2004й.

5. Рахметов Г.Р., Хорунов Ш.Р. и др. Теория дискретных устройств.

Методические указания. Ташкент, 2004г.

36