Ускорение направленного тестирования ПО путем учета потока данных при ограничении вариативности

реклама

Ускорение направленного

тестирования ПО путем учета

потока данных при

ограничении вариативности

траекторий выполнения

А. С. Щербаков

ЗАО «Интел А/О»

Содержание

•

•

•

•

•

•

•

•

•

•

Обзор базового алгоритма тестирования - DART

Первичные и повторные обходы путей

Зависимости данных в планировании путей

Комбинирование стратегий и приоритизация

Сбор зависимостей данных

Учет использований данных

Проблема недостижимых путей

Замечания по деталям реализации алгоритма

Результаты

Заключение

Intel

2

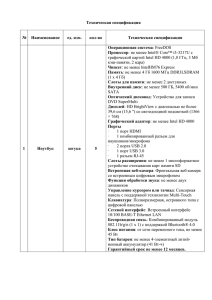

Пример DART. Тестируемый код

void f (int x, int y) {

if (x > y) {

x = x + y;

y = x – y – 3;

x = x – y;

}

x = x – 1;

if (x > y) {

abort ();

}

}

int main () {

const int x = choose_int ("x");

const int y = choose_int ("y");

f (x, y);

return 0;

}

• Процедуры системы тестирования

Intel

3

Пример DART. Шаг 1

x=0

y=0

нет

x<y

x1 = x – 1; =-1

нет

x1 > y

Intel

4

Пример DART. Шаг 2

нет

решения

нет

x<y

x1 = x – 1;

да

x1 > y

недостижимый

путь

Intel

5

Пример DART. Шаг 3

x=0

y=1

x<y

x1 = x + y;

y1 = x1 – y;

x2 = x1 – y1 – 3;

x3 = x2 – 1;

x1 = x – 1;

x1 > y

да

=1

=0

=-2

=-3

нет

x3 > y1

Intel

6

Пример DART. Шаг 4

x=0

y=9

x<y

=9

x1 = x + y;

y1 = x1 – y;

x2 = x1 – y1 – 3;

x3 = x2 – 1;

x1 = x – 1;

x1 > y

да

=0

=6

=5

x3 > y1

да

Ошибка

Intel

7

Философское замечание

•

В отличие от большинства

методов статического

анализа, оперирующих

конструкциями кода и его

графом управления, в

нашем подходе мы большей

частью рассматриваем

выполнение программы как

блуждание по тропкам леса

в поисках волшебного зверя

бага в программе

Intel

8

Первичные обходы vs. повторные

•

•

•

Первичный обход ветви – первое в прогоне набора

тестов “срабатывание” соответствующего условия

перехода с передачей управления на данную ветвь.

Реализуется в первую очередь, т.к. приводит к

росту покрытия

Nперв ~ N условий

Повторные обходы в различных комбинациях дают

разнообразные пути присваиваний переменных, в

результате могут быть созданы условия для новых

первичных переходов

Nповт ~ exp(N условий)

В среднем, количество обнаруженных ошибок

приблизительно пропорционально покрытию кода.

Intel

9

Ограничение повторных обходов

•

•

•

Идея ограничения повторных обходов:

Чтобы обнаружить баг, вероятно, достаточно

изменить направление лишь небольшого числа

условных переходов в случайном прогоне теста

Новые присвоения данных – естественный

индикатор интереса к повторным обходам..

Строгое соответствие Зависимость данных –

повторные обходы не всегда эффективно:

<<< Комбинаций присваиваний может быть

(экспоненциально) много

>>> Зависимость данных не всегда “видна”:

массивы, динамические ссылки, black boхеs,

волатильность, гонки..

Intel

10

Комбинирование стратегий

штраф

30

25

20

15

без зависимостей

10

1-3 зависимости

5

>3 зависимостей

0

1

•

3

5

7

9

11

13

15

17

19

21

23

25

27

29

число ПЧ

Решение: мягкое регулируемое ограничение

повторных обходов в зависимости от числа

обнаруженных зависимостей от новых

присваиваний

приоритизационный алгоритм

Intel

11

Сбор зависимостей данных

Стек ПВП

{v1,v2,v3}

Использов.

C2

L5

Присваив.

•

C4

H1

C4

H2

C7

H3

Для каждой значимой комбинации внутренних

переменных аккумулируется:

•

•

Множество использующих условий и участков кода

Таблицу записей (хеш стека присваиваний + номер

участка) для обнаруженных присваиваний

Intel

12

Пример программы

Intel

13

Пример: планирование тестов

Префикс пути

выполнения

№

1

Решение о

запуске теста

(непосещенная

ветвь/иная

причина)

Обнаруж.

использования

Входные переменные

a

b

0

c

()

Да (начало)

0

(C1=0;C2=0;C3=1)

Да (С3=1)

нет решения

(C1=0; C2=1)

Да (С2=1)

0

(C1=0;C2=1;C3=1)

Да (C3=1)

нет решения

(C1=1)

Да (С1=1)

1

(C1=1; С2=0;C3=1)

Да (C3=1)

нет решения

(C1=1,C2=1)

Да (в L2

используется новый

подстек для {x})

1

1

0

(C1=1,C2=1; C3=1)

Да (C3=1)

1

1

3

{x}

0

Обнаруж.

присваивания

{y}

C3

{x}

L0

{y}

L0

Подстек

присваивания

{x}

(L0)

{y}

(L0)

2

1

0

L2

(L0;L2) новый

L2

3

(L0;L1)новый

4

0

0

L1

(L0)

5

6

(L0;L2)

7

8

Intel

14

Учет использований

Необходимо знать

использования переменных в

произвольном конусе!

Обход CFG ?

сложность ~ Nузлов на каждое

принятие решения

Хранение копий для узлов ?

память ~ N2 узлов

Отказ от учета использований ?

Допустим в сочетании с

ограничением числа повторных

обходов ветвей при “быстром”

тестировании

Intel

15

Оптимизация учета

•

•

Ограничение числа учитываемых

используемых переменных в узле..

• Как правило, если в конусе используются

многие переменные, то и вероятность

использования произвольной переменной

велика

Хеширование

• Вносит вероятность избыточного

тестирования, но кардинально снижает

расходы

Intel

16

Хеширование использований

0001

0010

0100

0100

1000

0001

0110

1101

1111

Intel

17

Эффект маскирования путей

if (x)

print(“x=true”);

//неважно..

else

print (“x=false”);

//неважно..

x=F

x=T

if ((x & v) | y)

a = 1;

else

a = 3;

@ v=T,

w=F, y= F

if ((x & w) | y)

a = a * 2;

else

a = a * 5;

a = 15 a = 2

a=5

Intel

18

Эффект маскирования: учет

•

•

К счастью, мы явно знаем неудовлетворенные

условия и можем проверить их еще раз с новым

префиксом

• Список таких условий может быть велик, а

вероятность успеха мала..

Оптимизация: Рассматривать пересечение

текущего условия со всеми условиями

суффикса, повторно проверять только в случае

возможной импликации

• При ограничении сложности рассмотрения

логических форм, эффективно таргетирует

повторные проверки неудовлетворенных

путей суффикса

Intel

19

Альтернативы учета маскирования

•

•

•

Обход с ограничением комбинаций (Realernation

limit) даже при отсутствии зависимостей данных

• Вероятность покрытия невелика

Особое рассмотрение для “гамаков”

• “гамаки” могут содержать дополнительные

условия выхода/обхода

“Ожидание” “гамака”. Рассмотрение

ослабленного условия префикса

• Множество новых комбинаций, увеличенное

время теста, память

Intel

20

«Разворачивание» циклов

i>j

i>j

z=z+1

x=i+1

i>j

z=z+1

for (int i=0; i<=j; i++) {

x=i+1;

z++;

print (x);

}

i>j

Intel

21

“Перекрестные” использования

Использование

приоритетов →

порядок обходов

отличен от DFS

Учитываем

динамическое

добавление

использований из

конкурирующих

прогонов

Intel

22

Результаты

•

•

•

•

Метод применялся , в частности, при отладке

аппаратно-программного комплекса для

тестирования готовых кристаллов процессоров.

Быстрое тестирование с числом чередований

условий переходов более 30, нахождение

ошибок с вероятностью более 99% в примерах

Firmware и модульных тестов

Высокая эффективность при выявления

ошибок в программах тестирования СБИС,

встроенном ПО и программах обработки текста

на уровне регулярных выражений.

Для сложных арифметико-логических устройств

предпочтительнее специализированные

алгоритмы, не использующие перебор путей

Intel

23

Заключение

•

•

•

DART - универсальным метод тестирования ПО

для СБИС

• Мощность решателей (SMT solvers)

стремительно растет.

• Все же требуется кардинальное сокращение

обходов комбинаций ветвлений.

Комбинация ограничения повторных обходов с

учетом зависимости данных является умеренно

ресурсоемкой, но эффективной стратегией

быстрого достижения покрытия теста и

выявления ошибок

Алгоритм легко интегрируется с различными

эвристиками, ограничивающими число тестов

Intel

24