Лекция 4. Проблемы обеспечения надежности программ и

реклама

Институт системного программирования Российской академии наук

http://www.ispras.ru

Проблемы обеспечения

корректности программ и

аппаратуры

Камкин Александр Сергеевич

kamkin@ispras.ru

Московский физико-технический институт (государственный университет), 11 марта 2013 г.

Корректность и надежность

• Корректность – соответствие системы налагаемым

на нее требованиям

– Минимизация ошибок проектирования

• Надежность – способность системы сохранять

работоспособное состояние

– Минимизация сбоев при эксплуатации

•

(Корректность)

(Надежность)

– Ошибки – частая причина непредвиденных сбоев

Содержание лекции

Основная тема: обеспечение корректности микропроцессоров

• Введение

– Ошибки и их последствия

– Этапы проектирования

– Функциональная верификация

• Основные подходы

– Имитационная верификация

– Генерация тестовых программ

– Формальная верификация

• Проекты ИСП РАН

– Проекты C++TESK / MicroTESK

– Статический анализ и формальная верификация

– Актуальные проблемы

Цена ошибки проектирования

Вертолет Чинук CH-47, 1994

система управления двигателем

Боинг 757 (рейс 965), 1995

отображение информации

•

•

•

Комплекс ПВО Пэтриот, 1991

система наведения ракет

Человеческие жизни

> 100 млн долларов

Потеря репутации

Ракета-носитель Ариан 5, 1996

несовместимость SW/HW

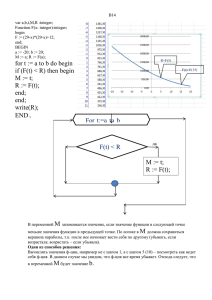

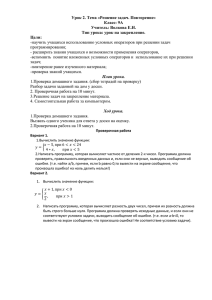

Статистика ошибок

Среднее число ошибок на 1000 строк кода

Intel

Среднее

Microsoft

NASA

Linux

0

10

20

30

40

50

60

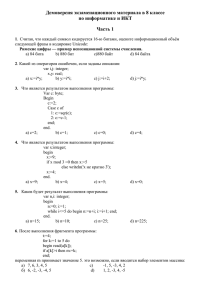

Сложность микропроцессоров

Микропроцессор

• > 109 транзисторов

• > 107 строк на Verilog

• ~4-10 ядер

Число транзисторов на кристалле (log10)

12.0

5 млрд (Xeon Phi)

22 нм

10.0

42 млн (Pentium 4)

180 нм

8.0

6.0

Проектирование

• > 500 разработчиков

• ~3-4 года работы

• > 100 млн долларов

3.1 млн (Pentium)

800 нм

29 тыс (8086)

3 мкм

2,2 тыс (4004)

10 мкм

4.0

2.0

0.0

1965

731 млн (Core i7)

45 нм

1970

1975

1980

1985

Число транзисторов

удваивается каждые 2 года

1990

1995

2000

2005

2010

2015

Верификация – более 60% затрат на проектирование микропроцессора!

• > 10 000 ошибок проектирования (в спецификациях, Verilog-коде и т.д.)

• > 100 инженеров-верификаторов (модели, тесты, формальные методы)

• > 1000 компьютеров (круглосуточное моделирование и прогон тестов)

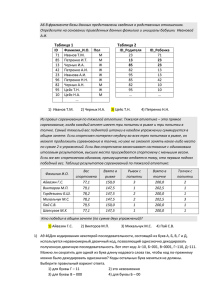

Проектирование микропроцессора

Требования

Архитектурное проектирование

Программный прототип (С/C++)

Верификация

Детальное проектирование

Модель уровня RTL (Verilog/VHDL)

Верификация

Логический синтез

Логическая схема

Верификация

Физический синтез

Фотошаблоны

Функциональная верификация

• Верификация – это проверка корректности,

соответствия реализации ее спецификации

– Экспертиза – непосредственный анализ результатов

проектирования: инспекция кода программы и т.п.

– Статический анализ кода – автоматическая проверка

заданных правил, поиск ошибок по шаблонам и т.п.

– Тестирование – оценка корректности системы по

результатам ее работы в некоторых ситуациях

– Формальная верификация – строгое доказательство

корректности формальной модели системы

Автоматизация верификации

Формальные модели,

спецификации, правила

Генерация

тестов

автоматы,

цепи Маркова

Проверка

поведения

Проверка

моделей

пред- и постусловия, автоматы,

временные логики

временные логики

Дедуктивный

анализ

Статический

анализ

аксиомы,

правила вывода

семантика языка,

шаблоны ошибок

Модульная и системная верификация

Модульная верификация

Системная верификация

Проверяется модель отдельного модуля

Проверяется модель всего микропроцессора

через входные и выходные сигналы

с помощью тестовых программ

lui

ori

lui

ori

add

sub

add

s1,

s1,

s3,

s3,

v0,

t1,

t7,

0x2779

s1, 0xc8b9

0x4ee

s3, 0xf798

a0, a2

t3, t5

s1, s3

Языки описания аппаратуры (HDL)

// Код Verilog

always @(posedge CLK)

input S;

begin

if(state == 2’h0 && S) begin

output

R1, R2;

state <= 2’h1;

<= 3’h6; {

voiddelay

design()

end

while(true) {

else if(state == 2’h1) begin

delaywait(S);

<= delay – 3’h1;

if(delay == 3’h0) begin

delay(6);

state

<= 2’h2;

R1

1’h1;

R1 =<=1;

end

delay(1);

end

else if(state

2’h2) begin

R1 ===0;

state <= 2’h3;

R2

1;

R1

<= =

1’h0;

R2

<= 1’h1;

delay(1);

end

R2 ===0;

else if(state

2’h3) begin

}state <= 2’h0;

R2

<= 1’h0;

}end

end

CLK

S

R1

R2

6 тактов

Параллельные присваивания

Поведение цифровой аппаратуры

Задачи имитационной верификации

Генерация стимулов

Проверка реакций

Оценка покрытия

Генератор

стимулов

Генератор стимулов

Тестовый оракул

Тестовое покрытие

Целевая

система

Тестовый

оракул

Тестовое

покрытие

Тестирование на основе моделей

Модель

системы

Генератор

стимулов

Целевая

система

Тестовый

оракул

Тестовое

покрытие

Преобразование интерфейсов

Входной интерфейс #1

Выходной интерфейс #1

Data

Data

Data

Data

Data

HDL

Data

Data

input <int> in;

Входной интерфейс #N

output<bool> out;

...

assert(i < MAX_SIZE);

Оракул

fifo[i++] = recv(in);

Адаптер входного

...

интерфейса

Эталонная

модель

send(out,

i == MAX_SIZE);

...

Выходной интерфейс #M

Адаптер выходного

интерфейса

Генерация тестовых программ

Целевая система

(HDL)

Тестовые программы

(ассемблер)

lui

ori

lui

ori

add

sub

add

s1,

s1,

s3,

s3,

v0,

t1,

t7,

0xdead

s1, 0x0

0xbeef

s3, 0xf

a0, a2

t3, t5

s1, s3

Трассы выполнения

(форматированный текст)

0x2000:

0x2004:

0x2008:

0x200c:

0x2010:

0x2014:

0x2018:

lui

ori

ori

lui

add

sub

add

...

...

...

...

...

...

...

0x2000:

0x2004:

0x2008:

0x200c:

0x2010:

0x2014:

0x2018:

lui

ori

ori

lui

add

sub

add

...

...

...

...

...

...

...

Эталонный симулятор

(C/C++)

Компаратор трасс

(Perl, Python)

Генерация тестов на основе моделей

Генератор на основе

моделей

Шаблон тестовой программы

Тестовая

программа

Модель

Variable: addr = 0x100

Resource Initial Values:

Модель

микропроцессора

Variable: reg

R6 = 8,

R3 = – 25,..., R17 = – 16

Bias: Resource-Dependency(GPR) = 30 100 = 7, 110 = 25,..., 1F0 = 16

Модель тестового покрытия

Bias: Alignment(4) = 50

Instructions:

Инженер по

Instruction:

Load R5 <- ?

500: Load R5 <- FF0

моделированию

Bias: Alignment(16) = 100

:

Генератор

Repeat (addr < 0x200)

504: Store R4 -> 100

Instruction: Store reg -> addr

508: Sub R5 <-Ядро

R6 –генератора

R4

Select

50C: Store R4 -> 110

Test templates

Test

templates

Instruction: Add ? <- reg

+ ? тестов

510: Add R6 <- R4

+ R3

Шаблоны

Библиотеки

Bias: SumZero

:

Instruction:

Sub ? <- ? – ?

Инженер

по

57C: Store R4 -> 1F0

addr

= addr + 0x10

верификации

580: Add R9 <- R4 + R17

Testprograms

programs

Test

Тестовые

программы

Формальная верификация

Целевая

система

Модель системы

Соответствие

Формальное

соответствие

~

Требования

Модель требований

Инструмент C++TESK

http://forge.ispras.ru/projects/cpptesk-toolkit

• Разработка моделей аппаратуры и адаптеров моделей на

языке C++

• Описание тестового покрытия и сценариев тестирования

• Генерация тестовой последовательности на основе обхода

графа состояний модели

• Распараллеливание прогона теста на основе

распределенного обхода графа состояний

• Генерация отчетов о тестировании

Инструмент MicroTESK

http://forge.ispras.ru/projects/microtesk

• Описание архитектуры микропроцессора на ADL

языке (Sim-nML)

• Конфигурирование типовых подсистем

• Извлечение тестовых ситуаций

• Описание шаблонов тестовых программ (Ruby)

• Генерация шаблонов тестовых программ на основе

моделей

Статический анализ HDL-описаний

always @(posedge CLK)

begin

if(state == 3’h0 && S) begin

state <= 2’h1;

delay <= 3’h6;

end

else if(state == 3’h1) begin

delay <= delay – 3’h1;

if(delay == 3’h0) begin

state <= 2’h2;

R1

<= 1’h1;

end

end

else if(state == 3’h2) begin

state <= 2’h3;

R1

<= 1’h0;

R2

<= 1’h1;

end

else if(state == 3’h3) begin

state <= 2’h0;

R2

<= 1’h0;

end

else if(state == 3’h4) begin

state <= 3’h0;

end

end

state

0

• Анализ потоков данных и зависимостей

• Извлечение автоматных моделей

1

delay = 0

• Автоматическая абстракция моделей

• Формальный анализ моделей

• Поиск зависаний и конфликтов

2

3

Недостижимое

• Генерация направленных тестов

состояние

4

Мертвый код

S

delay 0

A. Gotmanov, S. Chatterjee, M. Kishinevsky. Verifying Deadlock-Freedom of Communication Fabrics.

Анализ коммуникационных сетей

• Моделирование сетей на кристалле

• Вероятностный анализ работы сетей

• Доказательство отсутствия зависаний

• Генерация тестов по сетевым моделям

• Моделирование конвейеров

• Верификация многоядерных процессоров

Актуальные проблемы

• Автоматическая генерация функциональных тестов на

основе разного рода моделей

• Глубокий статический анализ Verilog-описаний цифровой

аппаратуры (потенциальные ошибки, мертвый код и т.п.)

• Автоматический поиск зависаний (deadlocks) в

микроархитектурных моделях процессоров

• Формальная верификация протоколов обеспечения

когерентности памяти в многоядерных процессорах

• Распараллеливание верификации, обработка больших

графов (генерация тестов и проверка моделей)

Основные работы отдела ТП

• Создание технологий и инструментов

–

–

–

–

Тестирование на основе моделей (UniTESK)

Проверка соответствия стандарту Linux Standard Base

Верификация драйверов Linux

Верификация микропроцессоров

• Разработка тестов и тестирование

–

–

–

–

–

–

Информационная система оператора связи

Операционные системы реального времени

Базовые библиотеки Linux (Linux Standard Base)

Сетевые протоколы IPv6, Mobile IPv6, IPsec

Отдельные модули компиляторов Intel

Микропроцессоры архитектуры MIPS / Elbrus

Контактная информация

• Институт системного программирования РАН (ИСП РАН)

http://www.ispras.ru

• Верификация микропроцессоров @ ИСП РАН

http://hardware.ispras.ru

• А.С. Камкин, к.ф.-м.н., с.н.с. ИСП РАН

kamkin@ispras.ru

Спасибо!