РРТ - МЦСТ

реклама

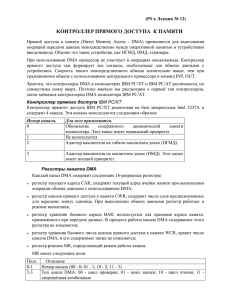

Выпускная квалификационная работа Разработка имитатора жесткого диска для верификации интерфейса PATA Выполнил: Фадеев Роман, ФРТК, 613 гр. Научный руководитель: Михайлов М.С. Южный мост вычислительных систем на базе микропроцессоров “Эльбрус-S”, “МЦСТ-4R“ (Структурная схема) • IOH — система для связи внешних устройств с CPU • SC – системный коммутатор • Контроллеры внешних интерфейсов объединены с помощью системного коммутатора и являются его абонентами. • Для обмена IOH с системой используется IO-link интерфейс. Этот же интерфейс используется для обмена между абонентами IOH и системным коммутатором SC. Постановка задачи Разработка имитатора интерфейса PATA (Parallel AT Attachment) для проверки работы PATA контроллера Требования • Имитатор должен удовлетворять требованиям спецификации AT Attachment with Packet Interface — 6 (ATA/ATAPI-6) • Поддержка режимов PIO, Multiword DMA, Ultra DMA • Тактовая частота 100 Мгц • Реализация команд передачи данных SET FEATURES, READ DMA, WRITE DMA, READ SECTROR(S), WRITE SECTOR(S) Структура имитатора С учетом требований поддержки режимов PIO, Multiword и Ultra DMA модель имитатора разбита на 4 части: • Command Block Registers – регистры управления интерфейсом • Блок управления передачей данных в режиме PIO • Блок управления передачей данных в режиме Multiword DMA • Блок управления передачей данных в режиме Ultra DMA Command Block Registers Command Block registers используются для передачи команд в устройство и приема статуса от уcтройства. Регистры: • LBA (High, Mid, Low) – задают адрес в буфере имитатора, размер буфера равен 2048 16-битных слов, что составляет 8 секторов (один сектор = 512 байт) • Sector Count – содержит число секторов для передачи • Command – содержит код команды для исполнения • Status, Alternate Status – содержат статус устройства • Features – содержит дополнительные параметры команды • Error – содержит ошибку • Data register – хранит передаваемое слово в PIO режиме • Device control register – управление прерываниями и software reset Команды, поддерживаемые имитатором • SET FEATURES задает режимы Multiword DMA и Ultra DMA с параметрами в регистре Sector count • READ/WRITE SECTOR(S) чтение/запись данныx в PIO режиме • READ/WRITE DMA чтение/запись данныx в DMA режиме Принципиальная схема работы имитатора в PIO режиме • Модель реализована с помощью state machine с четырмя состояниями pio_IDLE, pio_SEL, pio_READ, pio_WRITE • Работа в PIO режиме начинается с записи хостом команды READ SECTOR(S) или WRITE SECTOR(S). PIO протокол • PIO протокол используется в старых реализациях HDD, в имитатор включен из требований совместимости • Самый медленный режим передачи данных • Во время PIO передачи текущее передаваемое слово содержится в Data register Принципиальная схема работы имитатора Multiword режиме • Модель реализована с помощью state machine с шестью состояниями mwdma_IDLE, mwdma_PREP, mwdma_RD_TRANSFER, mwdma_WR_TRANSFER, mwdma_RD_TERMINATED, mwdma_WR_TERMINATED • Работа в Multiword режиме начинается с активации хостом Multiword режима и записи хостом команды READ DMA или WRITE DMA Multiword DMA • Стробы чтения/записи всегда генерируются хостом • Передача управляется связкой DMARQ и DMACK• Прерывание burst хостом – хост снимает DMACK• Прерывание burst имитатором – имитатор снимает DMARQ на переднем фронте DIOR-/DIOW- Реализация Ultra DMA в модели (специфика) Предварительные замечания 1) В режиме Ultra DMA некоторые сигналы исполняют другие функции и имеют другие названия (название указано после «:») • DIOR-: HDMARDY-: HSTROBE (Device I/O read: Ultra DMA ready: Ultra DMA strobe) • DIOW-: STOP (Device I/O write: Stop Ultra DMA burst) • IORDY: DDMARDY-: DSTROBE (I/O channel ready: Ultra DMA ready: Ultra DMA data strobe) 2) Данные передаются по обоим фронтам DSTROBE 3) Передача управляется двойной связкой DMARQ и DMACK-, STOP и DMARDY 4) Подсчет CRC Принципиальная схема работы имитатора в ULTRA DMA режиме Имитатор прерывает UltraDMA DMAIn In Burst Хост прерывает Ultra DMA In Burst Инициализация inBurst Установившийся Инициализация Ultra DMA out burst Установившийся Ultra DMA out burst Имитатор прерывает Ultra DMA out burst Хост прерывает Ultra DMA out burst UDMA CRC • Устройство, и хост имеют 16-битную CRC функцию и вычисляют значение CRC для каждого фронта STROBE • В конце Ultra DMA burst хост высылает свой результат CRC устройству на спадающем фронте DMACK-. Устройство сравнивает полученное CRC со своим собственным. Если значения не совпадают, то устройство сохраняет сведения об ошибке Реализация временных характеристик в модели • PIO t0 (cycle time) Режим 0 – 600 нс, 1 – 383 нс, 2 – 240 нс , 3 – 180 нс, 4 – 120 нс • Multiword t0 (Cycle time) Режим 0 - 480 нс, 1 - 150 нс, 2 - 120 нс • Ultra DMA t2cyctyp (Typical sustained average cycle time) Режим 0 – 240 нс, 1 – 160 нс, 2 – 120 нс , 3 – 90 нс ,4 – 60 нс, 5 – 40 нс Результаты • Разработано Verilog описание имитатора интерфейса PATA • Произведено тестирование в составе RTLмодели IOH • Обеспечена корректная работа во всех PIO, Multiword, Ultra DMA режимах Спасибо за внимание!