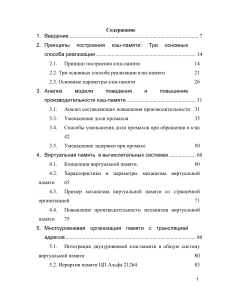

Кэш

реклама

Кэш Алгоритмы отображения • Прямой – 1 блок – 1 строка – Плюс: быстрый поиск, маленькие теги, простая реализация – Минус: пробуксовка кэша • (Полностью) ассоциативный – 1 блок – любая строка – Плюс: нет пробуксовки кэша – Минус: медленный поиск, большие теги, сложная реализация • Множественно-ассоциативный – 1 блок – несколько строк – Компромиссный вариант Увеличение производительности кэша • Цель: уменьшить среднее время доступа к памяти – -Time = Hit Time + Miss Penalty * Miss Rate • Подходы – Уменьшить Hit Time – Уменьшить или скрыть Miss Penalty – Уменьшить Miss Rate • Важно – Подходы могут конфликтовать между собой – Помнить о продолжительности такта, площади и энергопотреблении Причины кэш-промахов • «Холодные» промахи – Первый доступ к адресу – Случаются даже в бесконечных кэшах • Промахи из-за размера – Кэш слишком маленький, чтобы уместить данные – Промахи в полностью ассоциативном кэше определенного размера • Конфликтные промахи – Промахи из-за недостаточной ассоциативности – Два адреса, отображаемые на один блок в прямом кэше Какими должны быть основные параметры кэша? • Размер кэша – Большой, чтобы вместить рабочие данные – Маленький, для быстрого доступа • Степень ассоциативности кэша – Большая, чтобы избегать пробуксовки – Маленькая, для быстрого доступа • Размер строки кэша – Большой, чтобы использовать локальность – Большой, чтобы уменьшить теги – Маленький (много блоков меньше промахов, меньше задержки при промахе) Многоуровневые кэши • Идея – Оптимизировать разные кэши по разным параметрам – Использовать соотношение цена/качество на различных уровнях • Кэш 1-го уровня – Оптимизирован на быстрое время доступа – 8 – 64 Кб, Прямой – 4-х ассоциативный • Кэш 2-го уровня – Оптимизирован на низкую вероятность промаха – 256 Кб-4Мб, 4 – 16-и ассоциативный • Кэш 3-го уровня – Оптимизирован на низкую вероятность промаха – > 4МБ, множественно-ассоциативный Процессор Pentium 4, Xeon (Northwood) Itanium2 Opteron Программные регистры 8 целочисл. (32 бит), 8 веществ. (80 бит), 16 векторных (128 бит) 128 целочисл. (64 бит), 128 веществ. (82 бит), 64 предикатных (1 бит), 8 регистров ветвлений (64 бит), 128 прикладных регистра 16 целочисл. (64 бит), 8 веществ. (80бит), 16 векторных (128-бит) Аппаратные регистры целочисл. 128 (32 бит), веществ. 128 (128 бит) соответствуют программным Alpha 21264 PowerPC 970FX 32 целочисл. (64 бит), 32 веществ. (64 бит) 32 целочисл (64 бит), 32 веществ. (64 бит), 16 векторных (128бит) 40 целочисл., 120 веществ. 80 целочисл., 72 веществ. 32 + 48 целочисл., 32 + 48 веществ., 16 + 16 векторных Кэш данных L1 8 KB, 4-way, строка 64 B, 16 KB, 4-way, строка 64 B, 64 KB, 2-way, строка 64 B, 64 KB, 2-way, строка 64 B, 32 KB, 2-way, строка 128 B, Кэш команд L1 кэш трасс, 12 K микроопераций, 8-way 16 KB, 4-way, строка 64 B, 64 KB, 2-way, строка 64 B 64 KB, 2-way, строка 64 B, 64 KB, прямого отображения, Кэш L2 512 KB, 8-way, строка 64B, 256 KB, 8-way, строка 128B, 1 MB, 16-way, строка 64 B, Кэш L3 1.5 – 9 MB, 12-way, строка 128B, 1 – 4 MB, внешний, 512 KB, 8-way, строка 128B, Алгоритмы записи • Сквозная запись (write through) • Сквозная запись с буферизацией (write combining) • Обратная запись (write back) MESI – Протокол когерентности кэшей • M (Modified): Локальный процессор изменил строку. Это, в частности, означает, что копия единственная на все кэши • E (Exclusive): Строка не модифицирована и не загружена ни в один из остальных кэшей • S (Shared): Строка не модифицирована и возможно присутствует и в других кэшах • I (Invalid): строка не используется Алгоритмы замещения кэш-строк • Least Recently Used (LRU) • Most Recently Used (MRU) • Pseudo-Least Recently Used (PLRU) Алгоритм замещения Pseudo-LRU Виртуальная память Виртуальная память: задачи • Динамическое распределение памяти • Отображение виртуальных адресов на физические • Реализация защиты памяти Виртуальная память процесса Редко используемые страницы на диске Активные страницы в ОЗУ ОЗУ Внешняя память Подгрузка/выгрузка страниц Способы адресации виртуальной памяти • Страничный • Сегментный • Странично-сегментный Страничная адресация памяти Двухуровневая таблица страниц в Pentium Трехуровневая таблица страниц в Itanium 2 Translation Lookaside Buffer (TLB) Виртуальный адрес 63 Номер виртуальной страницы вирт. страница TLB Биты 0 Смещение физ. страница Номер физической страницы 63 Физический адрес Смещение 0 Сегментная адресация памяти Странично-сегментная адресация памяти