Планирование периферии кристалла в составе САПР для реализации технологии корпусирования ИС

реклама

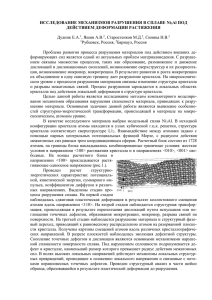

Планирование периферии кристалла в составе САПР для реализации технологии корпусирования ИС методом монтажа объемными выводами (FCP Die Planer) Магистерская диссертация студента ФРТК 218 гр. Федоткина Алексея Сергеевича Московский Физико-технический институт (государственный университет) Москва ● Июнь 2008 Технологии монтажа кристалла в корпус Проводной монтаж (Wires Bonding) контакты кристалла могут быть размещены только по периметру кристалла; отлаженная технология, есть САПР, рекомендации проектирования, технологические ограничения, стандарты. Монтаж объемными выводами кристалла на коммутационную плату корпуса (Flip-Chip) контакты кристалла могут быть размещены по всей поверхности кристалла; более новая технология, практически нет САПР, стандартов, недостаточно рекомендаций проектирования, технологических ограничений. Монтаж объемными выводами кристалла на коммутационную плату корпуса (Flip-Chip) Существующие САПР Synopsys Jupiter IO. Программа позволяет: разместить элементы в/в кристалла, и соответствующие контактные площадки; проверить размещение на наличие ошибок проектирования; получать информацию из базы данных Milkyway и сохранять результаты в БД Milkyway; Недостатки: требуется лицензия; не покрывается весь маршрут разработки корпуса. Cadence APD. Программа позволяет: разработать модель корпуса; назначить выводы кристалла на выводы корпуса; выполнить трассировку коммутационной платы; Недостатки: требуется лицензия; модель корпуса создается строится не по стандарту; трассировка коммутационной платы выполняется плохо; Сложно передать данные между САПР Synopsys и Cadence; Программы работают под разными ОС. САПР FCP В ОАО «ИНЭУМ» на основании государственного контракта на выполнение опытно-конструкторской работы «Разработка технологии создания матричных корпусов для СБИС с большим количеством выводов (в т.ч. для ВК «ЭЛЬБРУС») ведется разработка программы САПР FCP. Модуль Die Planer (FCP-DP), входит в состав САПР FCP. Программа должна выполняться на ПК с установленной ОС Linux или Windows в графическом или текстовом режиме. Принципиальные задачи планирование периферии кристалла; размещение контактных площадок объемных кристалла, согласно заданным шаблонам; поддержка элементной изготовления кристалла; базы для конкретной выводов технологии визуализация и редактирование элементов ввода-вывода кристалла и контактных площадок объемных выводов кристалла; проверка правил ограничений; проектирования, технологических совместимость форматов данных для обеспечения интеграции в другие САПР проектирования кристалла и разработки корпуса микросхемы; Структура программы Графический интерфейс (Java) Командный процессор (Java/Tcl) Java – C++ интерфейс Модуль управления изменяемыми настройками программы Модуль построения и редактирования выводов кристалла Модуль сообщений Внутренняя база данных Блок чтения / записи данных Модуль чтения Verilog Модуль чтения / записи TDF Модуль чтения / записи GDS Модуль чтения / записи DPF Модуль чтения TEC Применение FCP-DP в различных маршрутах проектирования TDF Synopsys ® Astro ™ Разработка кристалла GDS GDS или TDF, Verilog 1 Загрузка элементов в/в кристалла, с информацией о расположении и соответствующих контактных площадках Verilog 2 3 Загрузка элементов в/в кристалла, с информацией о расположении Загрузка списка элементов в/в кристалла Планирование периферии кристалла Технологический файл Формирование контактных площадок согласно заданным шаблонам DRC правила Визуализация, проверка DRC и ERC ERC правила Сохранение результатов DPF Дальнейшая разработка корпуса в САПР FCP FCP-DP TDF Планирование периферии кристалла: пользовательский интерфейс для ручного планирования периферии кристалла в виде двух диалоговых окон с таблицами: группировка одинаковых по назначению элементов в/в кристалла; размещение групп на кристалле; Автоматическое размещение контактных площадок объемных выводов кристалла Набор различных паттернов должен быть составлен для каждой используемой библиотеки элементов. Поэтому каждой библиотеке должен соответствовать свой технологический файл. Паттерны составляются на основании рекомендаций, описанных в документации, которая поставляется с библиотекой элементов. Технологический файл для поддержки библиотеки элементов Описание общих параметров используемой библиотеки (технологические ограничения): допустимые расстояния между контактными площадками, элементами в/в кристалла, расстояние до края кристалла; размер и форма контактных площадок; Описание шаблонов расстановки контактных площадок; Описание библиотечных элементов, используемых в конкретной технологии – размеры, тип. Пример технологического файла #Technology 90nm. Library technology file VERSION "libtec v.1" LIBRARY lib_90_tec TechnologyName PadCellPitch MinPadCellDistance BumpPadPitch MinBumpPadDistance BumpPadShape LayersBooFile END "TEC_90NM" 0 0 180 160 -10:-10 -10:10 "technology.boo" 10:-10 -10:-10 FILLERS MSD_PCORNER_SSTLC, MSD_PFEED_1_SSTLC, MSD_PFEED_5_SSTLC, MSD_PFEED1_SSTLC, MSD_PFEED5_SSTLC, MSD_PFEED10_SSTLC ALIAS LVDS_signal ALIAS LVDS_power ALIAS SSTL MSD_PVREF_SSTLC, MSD_PVAA_SSTLC #ALIAS SSTL_UNUSED ALIAS BIO PADCELLSSIZE 80 245 40 245 40 280 100 280 500 280 100 280 500 280 10 280 280 280 END LVDS_signal LVDS_power, BIO SSTL MSD_PFEED_1_SSTLC MSD_PFEED_5_SSTLC MSD_PFEED1_SSTLC MSD_PFEED5_SSTLC MSD_PFEED10_SSTLC MSD_PCORNER_SSTLC PATTERN pLDVS_2x245_80_80 PadCellsPitch 0 LVDS_signal LVDS_signal END 80:520 80:160 0:340 0:700 LVDSDRVR, LVDSRCVR PVDDIO, PVSSIO, PVDDC, PVSSC MSD_PDDRIO_SSTLC, MSD_PVDDQ_SSTLC, MSD_PVSSQ_SSTLC, MSD_PVDD_SSTLC, MSD_PVSS_SSTLC, MSD_PAIO_SSTLC, MSD_PDIFF_SSTLC BD25LVST_2_A, BD25LV_16_A Визуализация и редактирование Проверка правил проектирования проверка DRC и ERC: технологические ограничения; проверка правильности размещения элементов типа filler, corner, breaker, end-cap, согласно документации на используемую библиотеку элементов; прореживание элементов элементами питания и земли; в/в кристалла некоторые элементы в/в кристалла должны находиться рядом с конкретными функциональными элементами, согласно документации на используемую библиотеку элементов; прочие правила и рекомендации. Поддержка форматов входных / выходных данных Verilog – функциональное описание кристалла. GDS (Graphic Data System) – бинарный формат для представления топологии кристалла. Создается средствами САПР проектирования кристалла и содержит конечную выходную информацию о спроектированном кристалле. TDF (Top Design Format) – текстовый формат, представляющий собой командный файл. Разработан фирмой Synopsis. Содержит информацию о расположении библиотечных элементов кристалла и их название. DPF (Die Planer Format) – текстовый формат для передачи информации о кристалле в другие компоненты программного комплекса САПР FCP. TEC – технологический файл для САПР FCP, который содержит информацию о технологических ограничениях, элементах в/в кристалла, шаблонах размещения объемных выводов и т.д. Заключение 1. Реализована программа, позволяющая размещать элементы в/в кристалла, автоматически расставлять контактные площадки объемных выводов. Программа работает на ПК с ОС Linux или Windows с установленной средой исполнения Java версии не ниже 1.4; 2. Реализован графический интерфейс для визуализации элементов в/в кристалла; 3. Реализована автоматическая проверка правил DRC; 4. Изучена технологическая информация, правила проектирования для библиотеки элементов Synopsys на 90 нм. Составлен формат технологического файла и написан технологический файл для поддержки этой библиотеки; 5. Реализована совместимость форматов данных для интеграции программы в другие САПР; Реализованная программа используется при корпусов микропроцессоров Elbrus в ОАО «ИНЭУМ». разработке Визуализация кристалла Elbrus-3M Дальнейшее развитие программы 1. Полная автоматизация планирования периферии кристалла с учетом списка сигналов на печатной плате; 2. Добавление и поддержка новых правил DRC и ERC; 3. Улучшение программы. графического интерфейса Спасибо за внимание