Логические схемы одноразрядного двоичного сумматора на 3

реклама

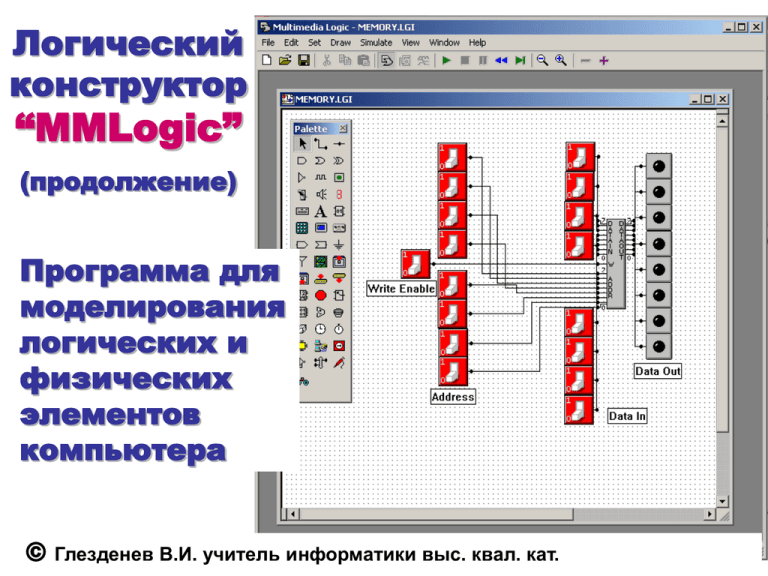

Логический конструктор “MMLogic” (продолжение) Программа для моделирования логических и физических элементов компьютера © Глезденев В.И. учитель информатики выс. квал. кат. Триггер — это электронная схема, широко применяемая в регистрах компьютера для надёжного запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния, одно из которых соответствует двоичной единице, а другое — двоичному нулю. Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров. Работа триггера Если данная схема не работает с узлами, то попробуйте сделать ее без узлов. Данные схемы реализовать в программе MMLogic Работа с текстом. Для того, чтобы работал селектор с текстовым файлом, необходимо: а) набрать текст (желательно 16 строк 0-15) и его сохранить; б) установить текстовое окно, ПКМ – Properties: Multiple и связь с файлом (Browse…) в) установить соответствующую связь, при щелчке мышкой по селектору будет отображаться строка, показывающая стрелкой. Данные схемы реализовать в программе MMLogic АЛУ в действии Данные схемы реализовать в программе MMLogic Селектор, изображение, клавиатура и дисплей. Настройка элемента изображение на семейство рисунков осуществляется в свойствах (properties), аналогично тексту. Связь установить с рисунком SLOT0 Рисунки взять на сервере: логика – MMLogic - Pic_Logic и скопировать себе в папку (все от 0 до 15) Данные схемы реализовать в программе MMLogic Датчик случайных чисел Случайное изображение. Данные схемы реализовать в программе MMLogic Логическая схема одноразрядного двоичного сумматора на два входа 1 (полусумматор) Логическая схема одноразрядного двоичного сумматора на 2 входа (полуссуматор). Таблица истинности: Данную схему реализовать в программе MMLogic A 0 0 1 1 B 0 1 0 1 S 0 1 1 0 P 0 0 0 1 Условное обозначение одноразрядного двоичного сумматора на три входа Сумматор служит, прежде всего, центральным узлом арифметико-логического устройства компьютера, однако он находит применение также и в других устройствах компьютера. Логические схемы одноразрядного двоичного сумматора на 3 входа. Таблица истинности: с с A 0 0 B 0 0 C 0 1 S 0 1 P 0 0 0 0 1 1 1 0 0 1 0 1 0 1 0 1 0 1 1 0 1 1 0 0 0 1 1 1 1 1 1 1 Логические схемы одноразрядного двоичного сумматора на 3 входа. Реализация схемы б) в MMLogic схему в) реализовать самостоятельно Сумматор — это электронная логическая схема, выполняющая суммирование двоичных чисел Многоразрядный двоичный сумматор, предназначенный для сложения многоразрядных двоичных чисел, представляет собой комбинацию одноразрядных сумматоров. Схема вычисления суммы C = (с3 c2 c1 c0) двух двоичных трехразрядных чисел A = (a2 a1 a0) и B = (b2 b1 b0) имеет вид: Сумматор двух трехбитных числа: А (а0, а1, а2) и В (b0, b1, b2): первым идет сумматор на 2 входа, все остальные - на 3 входа: a0 a1 b0 s a2 b1 b2 s s c2 c1 c0 Таблица истинности: p p p c3 a2 a1 a0 b2 b1 b0 c3 c2 c1 c0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 (Рассмотрены не все 0 0 1 0 0 1 0 0 1 0 варианты) 0 1 1 1 0 1 0 1 1 1 0 1 0 1 1 1 0 1 0 0 Данную схему реализовать в программе MMLogic самостоятельно Действие счетчика на 4 бита. Данные схемы реализовать в программе MMLogic Каскад из 3-х счетчиков на 4 бита. 0 разряд 1 разряд 2 разряд Данные схемы реализовать в программе MMLogic Работа 8-ми разрядного элемента памяти Внимание! Данную схему можно не собирать. Постоянно меняющееся случайное изображение. Каскад счетчиков служит замедлителем смены рисунка. Данные схемы реализовать в программе MMLogic