Организация ЭВМ

реклама

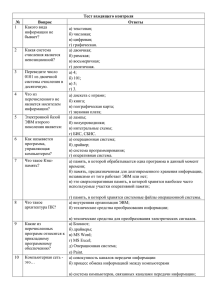

III.Организация памяти ЭВМ

• Классификация памяти ЭВМ. Характеристики

памяти.

• Методы организации доступа в

запоминающие устройства.

• Состав, устройство и принцип действия

основной памяти.

• Статические и динамические запоминающие

устройства. Организация кэш-памяти.

• Постоянные запоминающие устройства

(ПЗУ).

• Виртуальная память.

Организация ЭВМ

ИУ6

1

Памятью ЭВМ называется совокупность устройств,

служащих для запоминания, хранения и выдачи

информации.

Характеристики памяти ЭВМ:

-Назначение.

-Информационная емкость.

-Информационная емкость читаемого слова.

-Способ доступа.

-Быстродействие.

-Физический способ хранения информации.

Организация ЭВМ

ИУ6

2

Классификация запоминающих устройств по

способу доступа.

- Адресные ЗУ

Постоянные ЗУ, ПЗУ (ROM)

ЗУ c произвольным доступом (RAM)

- Ассоциативные ЗУ

Полностью ассоциативные ЗУ

Ассоциативные ЗУ с прямым размещением

Наборно-ассоциативные ЗУ

- Последовательные ЗУ

FIFO

LIFO

Файловые

Циклические

Организация ЭВМ

ИУ6

3

Классификация запоминающих устройств по

назначению.

ЭВМ

Быстродействие

Процессор

Управляющая память

Регистровая память

СОЗУ

Буферная память

Местная память

контроллеров

Емкость

Оперативная

память

Внешняя память

Организация ЭВМ

ИУ6

4

Обобщенная схема адресного ЗУ

Блок усилителей

записи

Принять адрес

Шина

адреса

Регистр адреса

0

Блок адресной

выборки

K-1

Регистр данных

Запись

Запоминающий

массив

N-1

Блок управления

Чтение

памятью

Блок усилителей

считывания

Принять данные

Выдать данные на ШД

Операция

Организация ЭВМ

ИУ6

5

Шина

данных

Обобщенная схема ассоциативного ЗУ

Регистр ассоциативного

признака

0

K

Запоминающий

массив

N-1

0

N-1

Принять С

Принять ШВХ

Принять ЗМ

Выдать на ШВЫХ

Выдать в ЗМ

Организация ЭВМ

Регистр информации

Принять АП

Выходная шина данных

ИУ6

6

Схема подсчета

K

Блок

управления

0

K

Регистр

совпадения

Регистр маски

0

Комбинационная

схема

Принять АП

Принять М

Входная шина данных

a0

a1

a2

Обобщенная схема последовательного ЗУ

Стек (память типа LIFO)

Шина данных

Счетчик

адреса

свободной

ячейки

Адрес

Операция

Адресное

запоминающее

устройство

Операция

Полон/Пуст

Организация ЭВМ

ИУ6

7

Буфер (память типа FIFO)

Шина данных

Адрес первой

Адрес

Адрес последней

Операция

+1 (Чтение)

+1 (Запись)

Адресное

запоминающее

устройство

Блок управления

памятью FIFO

Операция

Полон/Пуст

Организация ЭВМ

ИУ6

8

Адресные запоминающие устройства

Постоянные ЗУ, ПЗУ (ROM)

МПЗУ (MROM)

ППЗУ (PROM)

РПЗУ-УФ (EPROM)

ОПРПЗУ-УФ (EPROM-OTP)

РПЗУ-ЭС (EEPROM)

FLASH

ЗУ c произвольным доступом (RAM)

Динамические ЗУПД (DRAM)

Использующие кучность

адресов

FPM DRAM

EDO DRAM

BEDO DRAM

SDRAM

DDR SDRAM

RDRAM

Не использующие кучность

адресов

DRAM

RLDRAM

Статические ЗУПД (SRAM)

Асинхронные

Синхронные

Организация ЭВМ

ИУ6

9

Организация запоминающих массивов

адресных ЗУ

Структура ЗМ типа 2D

DC

ЗЯ

n

A

...

A[1..n]

CS

CS

ЗЯ

...

ЗЯ

...

...

...

ЗЯ

БУС

Количество выходов

дешифратора равно

количеству слов в

памяти (2n)

Структура применима

только для

малоразмерных ЗУ

Слово данных

Организация ЭВМ

ИУ6

10

Структура ЗМ типа 3D

A[n/2+1..n]

Адрес делится на две

части (двухкоординатная

выборка).

Количество выходов

дешифраторов: 2n/2+2n/2

n/2

DCy

DCx

ЗЯ

n/2

A

...

A[1..n/2]

CS

CS

...

ЗЯ

...

...

A[n/2..n] n/2

DCy

...

ЗЯ

ЗЯ

DCx

n/2

...

A

1

БУС

ЗM[1]

A[1..n/2]

1

ЗM[0] БУС

CS

CS

БУС

...

1

1

1 бит

Организация ЭВМ

ЗM[k-1]

...

БУС

Сл

ИУ6

11

ов

о

Структура ЗМ типа 2DM

DCx

A[1..n/2] n/2

CS

...

...

БУС

A

CS

ЗM[k-1]

ЗM[1]

ЗM[0]

БУС

БУС

MUX

MUX

...

MUX

A[n/2+1..n]

n/2

С

Мультиплексоры позволяют

выбрать один из 2n/2 разрядов

каждом из запоминающих

массивов

Организация ЭВМ

ИУ6

в

ло

о

- Размеры массивов близки

к оптимальным.

- Количество линий

записи/считывания

минимально.

12

Расслоение памяти

Блочное разделение адреса

A[n-2,n-1]

DC Банка

ЗМ[0]

A[0..n-1]

ЗМ[1]

ЗМ[2]

ЗМ[3]

A[0..n-3]

Номер банка

определяется старшей

частью адреса.

Буфер

Слово

Циклическое разделение адреса

A[0..1]

DC Банка

ЗМ[0]

A[1..n-1]

ЗМ[1]

ЗМ[2]

A[2..n-1]

ЗМ[3]

Номер банка определяется

младшей частью адреса

Буфер

Слово

Организация ЭВМ

ИУ6

13

Блочно-циклическое разделение адреса

Банк [0]

Банк [1]

ЗМ [0]

ЗМ [1]

ЗМ [0]

ЗМ [1]

0

4

1

5

2

6

3

7

…

…

...

…

Блочно-циклический способ обеспечивает возможность

пакетной передачи и ускоряет доступ при кучности адресов

Пример разделения адреса в SDRAM (PIII, P4)

Старшая часть

номера

столбца

31

Номер строки

25 24

Номер строки

31

Организация ЭВМ

Номер

банка

13 12 11 10

Смещение в

пакете

(16 байт)

4

Старшая часть

номера

столбца

13 12

ИУ6

Младшая

часть номера

столбца

6

0

Смещение в

пакете (младшая

часть номера

столбца)

Номер

банка

7

3

5

0

14

Статические ЗУ с произвольной выборкой (SRAM)

Запоминающая ячейка статической памяти

RS- триггер

Линия

выборки

Еп

T5

T6

T3

T4

T1

Линия

считывания/

Усилитель

записи

считывания

Организация ЭВМ

ИУ6

T2

Линия

считывания/

записи

15

Запоминающая ячейка с двухкоординатной выборкой

Линия выборки 1

Линия выборки 2

RS- триггер

Bit

Bit

Запоминающая ячейка двухпортовой выборкой

Линия выборки 1

RS- триггер

Линия выборки 2

Bit2 Bit1

Организация ЭВМ

ИУ6

Bit1 Bit2

16

Микросхема статической памяти

1

БУЗ

2

...

3

4

DC

адреса

строки

A

Матрица ЗЭ

Матрица

512 х ЗЭ

512

Матрица

512 х ЗЭ

512

4

Матрица

512 х ЗЭ

512

3

512 х 512

БУС

...

2

1

DC

адреса

столбца

WE

OE

CE

Организация ЭВМ

ИУ6

1

1

17

DO/DI

Диаграмма работы статической памяти

Адрес

слова

A

Адрес

слова

CE

RD/WE

OE

Считанные

данные

DO/DI

td

Организация ЭВМ

ИУ6

Записываемые

данные

ta

18

ПРИМЕР

Организация ЭВМ

ИУ6

19

ПРИМЕР

Организация ЭВМ

ИУ6

20

ПРИМЕР

Организация ЭВМ

ИУ6

21

ПРИМЕР

Организация ЭВМ

ИУ6

22

ПРИМЕР

Организация ЭВМ

ИУ6

23

ПРИМЕР

Организация ЭВМ

ИУ6

24

ПРИМЕР

Организация ЭВМ

ИУ6

25

ПРИМЕР

Организация ЭВМ

ИУ6

26

ПРИМЕР

Организация ЭВМ

ИУ6

27

Динамические ЗУ с произвольной

выборкой (DRAM)

DRAM для обращения по произвольным адресам

DRAM, RLDRAM

DRAM, оптимизированные для обращения по последовательным адресам:

FPM DRAM, EDO DRAM, BEDO DRAM, SDRAM, DDR SDRAM, RDRAM

При выборке строки

все Cз подключаются к

линиям считывания.

После считывания

необходимо

произвести обратную

запись информации –

регенерацию.

Заряд до 105 – 106

электронов.

Организация ЭВМ

ИУ6

Линия выборки

Сз

Линия

считывания

28

Процесс считывания в DRAM

Линия выборки

Заряд линии

Uп/2

Линия

считывания

Чтение 1

Сз

dU

Uп/2

dU

Сл

Сз << Сл

Откратие

транзистора

Усилитель

считывания

Организация ЭВМ

ИУ6

29

Чтение 0

Принцип действия усилителя-регенератора

Заряд линий

Подготовка

ЗЭ

Усилитель-регенератор

Еп

Uп/2

ЗЭ

T5

T6

Линия 2

Усилитель

регенератор

Линия 1

T1

T2

ЗЭ

ЗЭ

Организация ЭВМ

ИУ6

30

Контроллер динамической памяти

G

Сигнал синхронисации

1

C

HLDA

CTR

+1

D

R

T1

C

CTR

+1

D

Разр.

Запрос регенерациии

D

R

C

T2

HOLD

D

1

Регенерация завершена

R

Запр.

Адрес строки при

регенерации

A

0

1

A

RAS

C

MUX

A

RAS

CAS

WE

OE

&

1

CAS

&

&

Организация ЭВМ

ИУ6

31

DRAM

D

DO/DI

Буфер строки и

контроллер

регенерации

Регистр

адреса

Декодер

строки

Декодер

столбца

Буфер столбца

Банк 1

Банк 2

Усилителирегенераторы

A

Банк 0

Банк 3

Входной

буфер

Схема выбора

банка

DI

Выходной

буфер

Микросхема динамической памяти

DO

Сигналы управления

Регистр управления

CK,CK CKE CS

Регистр

программирования

Схема управления

латентностью и длиной пакета

WE RAS CAS DM

Организация ЭВМ

ИУ6

32

Функциональные возможности SDRAM памяти:

Декодер

Усилитель

Буфер

Организация ЭВМ

- Многобанковая огранизация.

- Командный режим работы.

- Команды пакетного чтения/записи.

- Использование чередования банков при

последовательном увеличении адресов.

- Команды пакетного чтения/записи с авторегенерацией.

- Возможность осанова чтения/записи по режиму

регенерации.

- Возможность останова чтения/записи по новому запросу

чтения/записи.

- Управление маскированием шины данных по сигналу

DQM.

- Минимальное время (1 CLK) между последовательными

командами.

- Команда PrechargeAll.

- CAS латентность 2 и 3 CLK.

- Длина пакета 1,2 и 4 слова.

- Команда саморегенерации.

- Режим энергосбережения.

ИУ6

33

Диаграмма работы DRAM памяти

tRCD

tCAC

tRP

RAS

CAS

A

WE

Адрес

строки

Адрес

столбца

Адрес

строки

Адрес

столбца

Чтение

Запись

D

Данные

Данные

tRCD – RAS to CAS Delay.

tRP – RAS Precharge.

tCAC – CAS Delay.

Организация ЭВМ

ИУ6

34

Способы повышения производительности RAM

- Синхронизация.

- Конвейеризация.

- Пакетный режим обмена.

- Ускорение реверса шины.

- Чередование банков при обращении по

последовательным адресам.

- Удвоение скорости.

Организация ЭВМ

ИУ6

Регистр DDR

35

Диаграмма работы FPM DRAM памяти

tRCD

t'<tRCD+tCAC

tCAC

tRP

RAS

CAS,

OE

A

Адрес

строки

WE

Адрес

столбца

Адрес

столбца

Чтение

D

Организация ЭВМ

Данные

Данные

ИУ6

36

Диаграмма работы BEDO DRAM памяти

tRCD

tCAC

tRP

t'<tRCD+tCAC

RAS

CAS,

OE

A

Адрес

строки

WE

Адрес

столбца

Чтение

D

Организация ЭВМ

Данные

ИУ6

Данные

Данные

Данные

37

Диаграмма работы SDRAM памяти

tCL

tRCD

t'<tRCD+tCAC

RAS

CAS

A

Адрес

строки

Адрес

столбца

Чтение

WE

DQM

CKE

CS

Пакет

D

Данные

Данные

Данные

Данные

C

Формула памяти: 4-1-1-1

Организация ЭВМ

ИУ6

38

Диаграмма работы DDR SDRAM памяти

Активация

строки

tRCD

Чтение

CL=2

tCL

RAS

CAS

A

Адрес

столбца

Адрес

строки

WE

DQS

0

D

2

1

C

Организация ЭВМ

ИУ6

39

3

Сравнение EDO RAM, SDRAM, DDR SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

40

Сравнение DDR и DDR2

DDR память

DDR2 память

200 МГц

200 МГц

Оперативная

память

200 МГц

Буферы

DDR

(200 МГц)

400 МГц

Процессор

200 МГц

Оперативная

память

200 МГц

200 МГц

200 МГц

Буферы

DDR

(400 МГц)

200 МГц

Организация ЭВМ

ИУ6

41

800 МГц

Процессор

Сравнение DDR и DDR2: SDR SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

42

Сравнение DDR и DDR2: DDR SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

43

Сравнение DDR и DDR2: DDR2 SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

44

Диаграмма состояний УА DDR SDRAM

Организация ЭВМ

ИУ6

45

Контроллер DDR/DDR2

ADR_IN[1 .. 0]

ADR_IN[31..0]

DATA_IN[127..0]

CMD[2..0]

CMD_VLD

ADR_IN[1 .. 0]

BANK[1 .. 0]

Контроллер

банка 0

Автомат

состояния банка

Счетчики

таймингов

CS1

Контроллер

банка 1

Автомат

состояния банка

Счетчики

таймингов

CS2

Контроллер

банка 2

Автомат

состояния банка

Счетчики

таймингов

CS3

Контроллер

банка 3

Автомат

состояния банка

Счетчики

таймингов

CS0

DDR PHY блок

Блок обработки запросов

COLUMN[12..0]

ROW[12..0]

DATA_IN[127..0]

CMD[2..0]

CMD_VLD

BANK[1..0]

Очередь запросов

к памяти

Менеджер

синхронизации

Планировщик

запросов

Организация ЭВМ

RASn

CASn

WEn

AQ

DQ

DQS

DM

CSn

CKE

CK

CKn

BE

CLK_FB_OUT

CLK_FB_IN

ИУ6

46

Отличие DDR и SDR DRAM

Организация ЭВМ

ИУ6

47

Тайминг памяти:

tCL-tRCD-tRP-tRAS

•

CAS Latency (tCL) - задержка в тактах между подачей сигнала CAS и

непосредственно выдачей данных из соответствующей ячейки. Одна из

важнейших характеристик любого модуля памяти;

•

RAS to CAS Delay (tRCD) - количество тактов шины памяти, которые

должны пройти после подачи сигнала RAS до того, как можно будет

подать сигнал CAS;

•

Row Precharge (tRP) - время закрытия страницы памяти в пределах

одного банка, тратящееся на его перезарядку;

•

Activate to Precharge (tRAS) - время активности строба. Минимальное

количество циклов между командой активации (RAS) и командой

подзарядки (Precharge), которой заканчивается работа с этой строкой,

или закрытия одного и того же банка.

Примеры таймингов памяти DDR: 2-2-2-5; 2.5-3-3-7

Примеры таймингов памяти DDR2: 3-3-3-9, 4-4-4-12 и 5-5-5-15

Организация ЭВМ

ИУ6

48

Сравнение DDR SDRAM CL=2 и CL=3

ПРИМЕР

Организация ЭВМ

ИУ6

49

Диаграмма состояний УА DDR SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

50

Команды DDR SDRAM

ПРИМЕР

Организация ЭВМ

ИУ6

51

ПРИМЕР

Организация ЭВМ

ИУ6

52

ПРИМЕР

Организация ЭВМ

ИУ6

53

ПРИМЕР

Организация ЭВМ

ИУ6

54

ПРИМЕР

Организация ЭВМ

ИУ6

55

ПРИМЕР

Организация ЭВМ

ИУ6

56

ПРИМЕР

Организация ЭВМ

ИУ6

57

ПРИМЕР

Организация ЭВМ

ИУ6

58

ПРИМЕР

Организация ЭВМ

ИУ6

59

ПРИМЕР

Организация ЭВМ

ИУ6

60

ПРИМЕР

Организация ЭВМ

ИУ6

61

ПРИМЕР

Организация ЭВМ

ИУ6

62

ПРИМЕР

Организация ЭВМ

ИУ6

63

Постоянные запоминающие устройства

МПЗУ (MROM)

ППЗУ (PROM)

РПЗУ-УФ (EPROM)

ОПРПЗУ-УФ (EPROM-OTP)

РПЗУ-ЭС (EEPROM)

FLASH

NVRAM

FRAM

MRAM

Преимущества ROM по сравнению RAM:

-Аппаратная простота.

- Высокая плотность размещения ЗЭ.

- Энергонезависимость.

- Большое быстродействие.

Организация ЭВМ

ИУ6

64

Регистр адреса

Шина

адреса

Дешифратор адреса

Структура ПЗУ (ROM)

0

K-1

Запоминающий

массив

N-1

Регистр данных

Шина данных

Организация ЭВМ

ИУ6

65

МПЗУ

ЗЭ на диодах

ЗЭ на МОП транзисторах

ППЗУ

ППЗУ с плавкими

перемычками

Организация ЭВМ

ИУ6

ППЗУ с пережигаемым pn переходом

66

РПЗУ-УФ, ОПРРПЗУ-УФ (EPROM, EPROM-OTP)

МНОП транзистор

Si3N4

Сток

Затвор

Исток

p+

p+

n

Канал

Подложка

РПЗУ-ЭС (EEPROM), FLASH

МОП транзистор с плавающим затвором

Плавающий

затвор

Сток

Затвор

Исток

p+

p+

n

Канал

Организация ЭВМ

ИУ6

Подложка

67

NAND FLASH

Все транзисторы, кроме адресуемого, должны

быть открыты. Если на плавающем затворе есть

заряд, то транзистор не откроется и на линии бит

будет высокий уровень. В противном случае

сигнал будет низкого уровня.

+ Большая компактность

- Меньшее быстродействие

Организация ЭВМ

ИУ6

NOR FLASH

Линии слов невыбранных транзисторов находятся

под низким потенциалом (транзисторы закрыты), на

затворе выбранного транзистора высокий

потенциал. Если на плавающем затворе

выбранного транзистора есть заряд, то транзистор

не откроется и на линии бит будет уровень лог.

единицы.

- Меньшая компактность

+ Большее быстродействие

68

Накопитель на основе FLASH

Контроллер FLASH HUKE 163H

ПРИМЕР

NAND FLASH HY27UV08AG5M

Организация ЭВМ

ИУ6

69

ПЗУ типа NVRAM

Энергонезависимая память NVRAM (Non-Volatile Random Access Memory) –

это оперативная память LPSRAM (Low Power SRAM – статическое ОЗУ с

очень низким потреблением), сохраняющая данные независимо от наличия

основного питания благодаря наличию встроенной литиевой батареи для

резервного питания. Интегрированная схема контроля и переключения на

резервный источник питания (супервизор и коммутатор литиевой батареи)

гарантирует работоспособность памяти NVRAM и сохранение данных в

течение десяти лет при полном отсутствии внешнего питания.

Организация ЭВМ

ИУ6

70

ПЗУ на основе сегнетоэлектрической пленки

(FRAM)

+Высокая скорость записи

- Необходимость восстановления информации

при доступе

ПРИМЕР

Основа запоминающего устройства FRAM — это конденсатор,

представляющий собой две пластины с тонким слоем ферроэлектрика

между ними. Приложенный к обкладкам конденсатора потенциал

поляризует ферроэлектрик. Направление поляризации представляет собой

двоичную информацию, хранящуюся в ячейке. При повторном приложении

потенциала заряд, затрачиваемый на реполяризацию, будет зависеть от

того, совпадает направление электрического поля с тем, которое

поляризовало ферроэлектрик в прошлый раз, или нет. Если направление

поля не совпадает, то на изменение поляризации потребуется

значительный дополнительный заряд. Таким образом, если при повторном

наложении потенциала наблюдается электрический ток, то направление не

совпадает с предыдущим. По наличию или отсутствию тока перезаряда

можно судить о содержимом ячейки.

Организация ЭВМ

ИУ6

71

Магниторезистивные ПЗУ (MRAM)

ПРИМЕР

-+Сверхвысокое быстродействие (до 2-3 нс)

+Низкое энергопотребление

+Неограниченное количество циклов чт/зп

Проводимость магниторезистивного слоя зависит от магнитного поля, в

которое он помещен. Внутри запоминающего элемента MRAM сопротивление

находящегося в нем магниторезистивного материала будет определяться

ориентацией магнитных моментов ферромагнитных слоев. В одном из

магнитных слоев домены фиксированы в одном направлении. В другом слое

они в ответ на воздействие внешнего поля могут быть развернуты в

противоположном направлении. В результате они могут быть либо

параллельны, либо антипараллельны элементам фиксированного слоя. Эти

два состояния запоминают «1» или «0».

Организация ЭВМ

ИУ6

72

ПРИМЕР

Организация ЭВМ

ИУ6

73

ПРИМЕР

Организация ЭВМ

ИУ6

74

ПРИМЕР

Организация ЭВМ

ИУ6

75

ПРИМЕР

Организация ЭВМ

ИУ6

76

ПРИМЕР

Организация ЭВМ

ИУ6

77

ПРИМЕР

Организация ЭВМ

ИУ6

78

ПРИМЕР

Организация ЭВМ

ИУ6

79

ПРИМЕР

Организация ЭВМ

ИУ6

80

ПРИМЕР

Организация ЭВМ

ИУ6

81

ПРИМЕР

Организация ЭВМ

ИУ6

82

ПРИМЕР

Организация ЭВМ

ИУ6

83

ПРИМЕР

Организация ЭВМ

ИУ6

84

ПРИМЕР

Организация ЭВМ

ИУ6

85

ПРИМЕР

Организация ЭВМ

ИУ6

86

Принципы построения кэш-памяти

Кэш-память – ассоциативное ЗУ, позволяющее сгладить разрыв в

производительности процессора и оперативной памяти. Выборка из

кэш-памяти осуществляется по физическому адресу ОП.

Процессор

Контроллер кэш

Кэш

Hit

Оперативная

память

Организация ЭВМ

ИУ6

Эффективность кэш-памяти зависит

от:

- Емкости кэш-памяти.

- Размера строки.

- Способа отображения ОП в кэш.

- Алгоритма замещения

информации в кэш.

- Алгоритма согласования ОП и кэш.

- Числа уровней кэш.

87

Размер линейки

Вероятность промаха

Вероятность промаха

Емкость кэш-памяти

Емкость кэш-памяти

Размер линейки

Способы отображения ОП в кэш:

- Произвольная загрузка.

- Прямое размещение.

- Наборно-ассоциативный способ отображения.

Организация ЭВМ

ИУ6

88

Произвольная загрузка

(Fully associated cache memory, FACM).

Адрес строки FACM

определяется из условия

формирования наиболее

представительной выборки

Тег

Смещение

Тег

CMP

...

Блок

КЭШ

Адрес

Адрес

Адрес

Адрес

Адрес

ОП

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

...

Тег

CMP

...

Блок

...

1

Hit

Организация ЭВМ

ИУ6

89

Прямое размещение.

Адрес строки однозначно определяется по тегу (i = t mod k).

0

ОП

1

2

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

0

0

k-1

КЭШ

0

k-1

1

0

2

1

n-1 0

Тег

Организация ЭВМ

ИУ6

Строка

n-1

Смещение

90

0

…

K-1

Наборно-ассоциативная кэш-память

(Set associated cache memory)

КЭШ

0

3

1

2

k-1

ОП

Данные

Данные

Данные

0

2

3

Данные

Данные

Данные

0

1

2

3

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

Данные

0

n-1

Тег

Набор

0 k-1

0

Смещение

CMP

Блок

n-1

Тег

Набор 0

CMP

Hit[0]

Блок

Hit[k]

Тег

Hit[0]

...

DC

Блок

...

Тег

Набор k-1

Блок

Hit[k]

Тег

Банк i-1

Банк 0

Организация ЭВМ

1

ИУ6

91

Hit

Алгоритмы замещения

- Замещение немодифицированных данных.

- Рандомизированный алгоритм.

- Замещение наименее используемого (Least Recently Used, LRU)

Согласование ОП и кэш

-Метод сквозной записи (Write True).

-Метод сквозной записи с буферизацией (Write Combining).

-Метод обратной записи (Write Back).

Протокол MESI

Modified

Exclusive

Shared

Invalid

- Признак несогласованных данных.

- Признак согласованных данных.

- Признак согласованных данных в ВС.

- Признак отсутствия данных.

* - http://lwn.net/Articles/252125/

Организация ЭВМ

ИУ6

92

Разделение кэш-памяти

Процессор

-Кэш L1 дублирует L2 (inclusive).

-Кэш L1 дополняет L2 (exclusive).

Контроллер кэш

L1

Кэш L1

Hit

Контроллер кэш

L2

Доступ к массивам данным по

случайным адресам

L1D — 2^13 байт

L2D — 2^21 байт

Кэш L2

Hit

Оперативная

память

Организация ЭВМ

ИУ6

93

Виртуальная память

Механизм виртуализации адресного пространства позволяет:

-Увеличить объем адресуемой памяти.

-Использовать физическую память различного объема.

-Возложить на аппаратную составляющую механизмы доступа к ВЗУ

-Сгладить разрыв в производительности ОП и ВЗУ.

-Ускоряет доступ к данным по последовательным адресам.

-Способствует реализации защиты памяти.

Виртуальные системы строятся по трем принципам:

-Системы с блоками различного размера (сегментная организация).

-Системы с блоками одинакового размера (страничная организация).

-Смешанные системы (сегментно-страничная организация).

Организация ЭВМ

ИУ6

94

Страничная организация

Программа отображается в память равными блоками – страницами.

Преобразование логического адреса в физический осуществляется

с помощью таблицы страниц.

Преобразование логического адреса в физический реализуется в

устройстве управления памятью (Memory Manage Unit), который

определяет, находится ли страница в физической памяти

(попадение).

Виртуальный адрес

Физический адрес (попадение)

MMU

ЦП

КЭШ

ОП

ВП

Физический адрес (промах)

Адрес

Организация ЭВМ

Данные

ИУ6

95

Схема страничного преобразования

Базовый регистр таблицы страниц

Адрес таблицы страниц

V - признак присутствия

страницы в физ. памяти.

R - признак использования

страницы.

M - признак модификации.

A - признак права

доступа.

Логический адрес

Номер страницы

Смещение

+

Таблица страниц

V R M A Номер физ. страницы

V=1

+

Структура TLB

Номер лог. страницы V R M A Номер физ. страницы

V=0

ОП

Прерывание

Организация ЭВМ

ИУ6

96

Сегментная организация

Программа отображается в память блоками различного размера –

сегментами. Преобразование логического адреса в физический

осуществляется с помощью таблицы сегментов.

Базовый регистр таблицы сегментов

Логический адрес

Адрес таблицы сегментов

Сегмент

Смещение

+

Таблица сегментов

V R M A

Длина

Физ. адрес сегмента

V=1

+

V=0

Организация ЭВМ

ИУ6

Прерывание

ОП

97

Сегментно-страничная организация памяти

Программа отображается в память блоками различного размера –

сегментами, каждый из которых целое число страниц.

Преобразование логического адреса в физический осуществляется с

помощью таблицы сегментов и таблицы страниц сегмента.

Логический адрес

Базовый регистр таблицы сегментов

Адрес таблицы сегментов

+

Сегмент

Страница

Смещение

Таблица сегментов

Адреса таблиц страниц

+

Таблица страниц сегмента

V R M A Номер физ. страницы

V=1

+

ОП

Организация ЭВМ

ИУ6

98

Исследование расслоения динамической памяти.

Код профилируемой программы на языке C.

// ВЫДЕЛЕНИЕ ПАМЯТИ

p = (int*)_malloc64(Param_[3]); // АДРЕС КРАТЕН 64

for (int pg_size = Param_[2]; pg_size <= Param_[1]; pg_size += Param_[2])

{

Start_Count(); // Начало замера времени

volatile int x = 0;

for (int b = 0; b < pg_size; b += Param_[2])

for (int a = b; a < Param_[3]; a += pg_size)

x += *(int *) (int(p) + a);

Finish_Count();// Конец замера времени

}

Организация ЭВМ

ИУ6

99

Сравнение эффективности ссылочных и

векторных структур

Организация ЭВМ

ИУ6

100

Исследование эффективности предвыборки в

TLB

Организация ЭВМ

ИУ6

101

Использование оптимизирующих структур

данных

Организация ЭВМ

ИУ6

102

Конфликты в кэш-памяти

Организация ЭВМ

ИУ6

103