Е.В. МАРЬИНА Научный руководитель – А.О. ВЛАСОВ АДАПТАЦИЯ ТОПОЛОГИЧЕСКОГО РАЗМЕЩЕНИЯ ЭЛЕ-

реклама

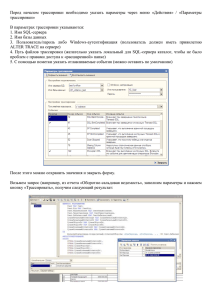

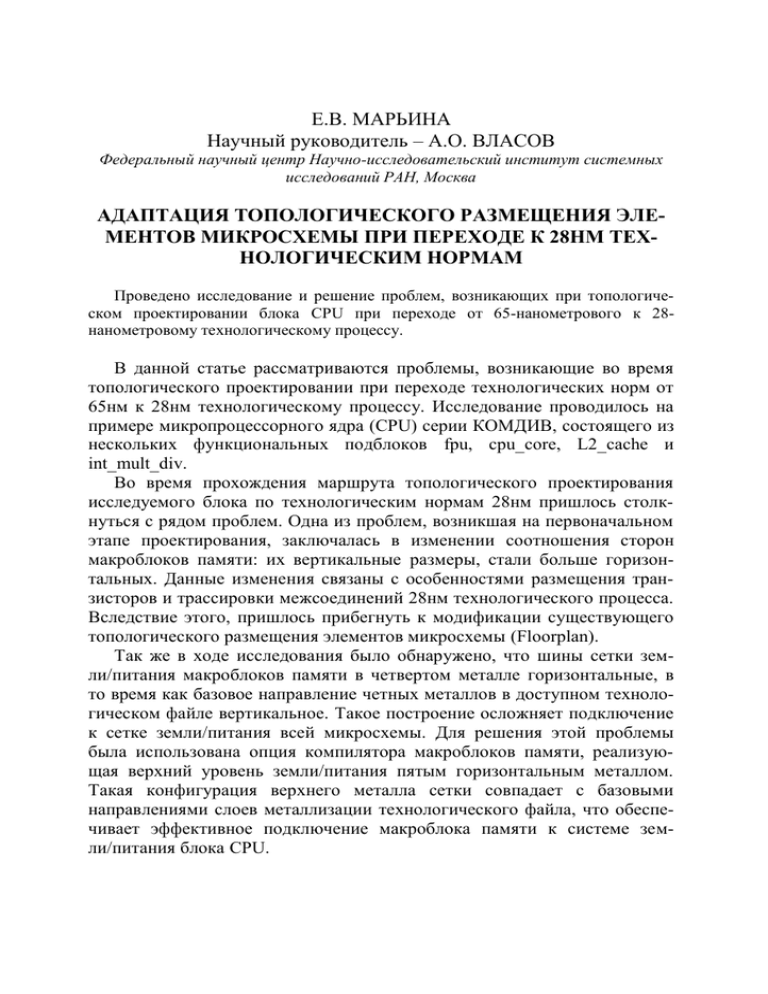

Е.В. МАРЬИНА Научный руководитель – А.О. ВЛАСОВ Федеральный научный центр Научно-исследовательский институт системных исследований РАН, Москва АДАПТАЦИЯ ТОПОЛОГИЧЕСКОГО РАЗМЕЩЕНИЯ ЭЛЕМЕНТОВ МИКРОСХЕМЫ ПРИ ПЕРЕХОДЕ К 28НМ ТЕХНОЛОГИЧЕСКИМ НОРМАМ Проведено исследование и решение проблем, возникающих при топологическом проектировании блока CPU при переходе от 65-нанометрового к 28нанометровому технологическому процессу. В данной статье рассматриваются проблемы, возникающие во время топологического проектировании при переходе технологических норм от 65нм к 28нм технологическому процессу. Исследование проводилось на примере микропроцессорного ядра (CPU) серии КОМДИВ, состоящего из нескольких функциональных подблоков fpu, cpu_core, L2_cache и int_mult_div. Во время прохождения маршрута топологического проектирования исследуемого блока по технологическим нормам 28нм пришлось столкнуться с рядом проблем. Одна из проблем, возникшая на первоначальном этапе проектирования, заключалась в изменении соотношения сторон макроблоков памяти: их вертикальные размеры, стали больше горизонтальных. Данные изменения связаны с особенностями размещения транзисторов и трассировки межсоединений 28нм технологического процесса. Вследствие этого, пришлось прибегнуть к модификации существующего топологического размещения элементов микросхемы (Floorplan). Так же в ходе исследования было обнаружено, что шины сетки земли/питания макроблоков памяти в четвертом металле горизонтальные, в то время как базовое направление четных металлов в доступном технологическом файле вертикальное. Такое построение осложняет подключение к сетке земли/питания всей микросхемы. Для решения этой проблемы была использована опция компилятора макроблоков памяти, реализующая верхний уровень земли/питания пятым горизонтальным металлом. Такая конфигурация верхнего металла сетки совпадает с базовыми направлениями слоев металлизации технологического файла, что обеспечивает эффективное подключение макроблока памяти к системе земли/питания блока CPU. Другая проблема геометрического планирования размещения была связана с особенностями использования второго металла при реализации стандартных ячеек по 28нм технологическому процессу. В них он используется для трассировки межсоединений и шин земли/питания. Данное обстоятельство, практически, лишает возможности его использования в процессе глобальной трассировки связей блока. Количество слоев металлизации, доступных для трассирования одинаково для 65нм и 28нм процессов. Таким образом, при 28нм нужно уменьшать локальную плотность стандартных ячеек для предотвращения проблем с трассировкой. Эту проблему также усугубляет «потеря» пятого металла для трассировки сигналов над макроблоками памяти, описанная выше. Так же для уменьшения плотности соединений элементов микросхемы некоторые из макроблоков памяти были расставлены в шахматном порядке. На рис. 1,а показан Floorplan исследуемого блока выполненный по технологии 65нм. Результатом данной работы является составленный Floorplan для технологического процесса 28нм (рис. 1,б), удовлетворяющий вышеупомянутым требованиям по предотвращению проблем, связанных с переходом на новый технологический процесс. S = 4,3мм x 3,3мм = 14,19мм2 S = 2,3мм x 2,4мм = 5,52мм2 а) б) Рис. 1. Floorplan блока CPU по технологии 65нм (рис.1,а) и обновленный Floorplan блока CPU по технологии 28нм (рис.1,б) Список литературы 1. Encounter® Foundation Flows: Hierarchical Implementation Flow Guide. Product Version 8.1.1 March 2009.