Департамент образования города Москвы Некоммерческая организация «Ассоциация московских вузов»

реклама

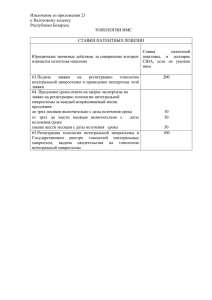

Департамент образования города Москвы Некоммерческая организация «Ассоциация московских вузов» Государственное образовательное учреждение высшего профессионального образования Московский государственный институт электронной техники (технический университет) Полное название вуза Научно-информационный материал для специалистов в области автоматизированного проектирования интегральных схем Разработка радиоэлектронной аппаратуры в области автоматизированного проектирования интегральных схем Москва 2009 г. Цель программы: привить основные навыки работы в САПР Cadence. Обучить методологии проектирования на схемотехническом, топологическом, системном, логическом и поведенческом уровне описания системы на кристалле. Изучение и практическое освоение САПР в области сквозного проектирования цифровых и аналоговых интегральных схем для современных электронных систем интегрального исполнения. привить основные навыки работы с языком Verilog-A в системе Cadence Краткое описание и содержание: Развитие науки и техники неразрывно связано с изучением современных автоматизированных программных сред проектирования интегральных микросхем. Специалист по разработке интегральных микросхем должен знать и уметь пользоваться современными программными продуктами, позволяющими ускорить процесс разработки цифровых и аналоговых устройств. Без навыков работы с интегрированной системой сквозного проектирования Сadence невозможно выполнять проектирование интегральных схем. Отладка и верификация функционирования систем на кристалле осуществляется с помощью систем высокоуровневого поведенческого моделирования. Для описания аналоговых блоков в таких системах обычно используются модели на языках Verilog-A, Verilog-AMS В настоящее время нет средств, обеспечивающих автоматическое преобразование электрической схемы в описание на языке высокого уровня и обратно. Основной принцип разработки поведенческих моделей – декомпозиция полной схемы и последовательная замена небольших схемных фрагментов их поведенческими описаниями. Современные средства моделирования обеспечивают возможность одновременного использования транзисторных и поведенческих моделей, поэтому результат такого последовательного замещения можно постоянно контролировать. Надо заметить, что создание адекватных поведенческих моделей сегодня стало самостоятельным разделом схемотехники, требующим отдельной специализации. Создание топологии (маскирующих слоев) - один из наиболее важных шагов в сквозном проектировании детализированные (завершающая конфигурации и часть), где относительное проектировщик позиционирование описывает каждого маскирующего слоя, который используется в изготовлении кристалла с помощью топологического редактора - Virtuoso Editing Layout. Физическая топология проекта связана с получением предельных параметров схемы при реализации некоторой функции (площади, быстродействия и мощности потребления), так как физическая структура определяет: крутизну транзисторов; паразитные емкости и сопротивления; и очевидно, площадь кристалла. С другой стороны, детализированная топология масок логических элементов требует очень интенсивного и отнимающего много времени усилия для выполнения проекта. Этап топологического проектирования требует больших экономических и временных затрат, чем любые другие этапы разработки. Для уменьшения временных затрат создаются специализированные библиотеки как отдельных элементов, так и общих фрагментов схемы. Основными задачами этапа топологического проектирования являются задача размещения и задача трассировки. Целью этого этапа является минимизация площади кристалла. Но стандартизация топологии при автоматическом проектировании предлагает не совсем оптимальные решения (возможно увеличение площади кристалла в 2-3 раза), поэтому необходим постоянный контроль со стороны разработчика топологии рассматриваемой ИС. Также на этапе топологического проектирования производится экстракция паразитных элементов (паразитные емкости, сопротивления, транзисторы, теристорные структуры), отрицательно влияющих на параметры и характеристики данной ИС. По окончании разработки топологии ее необходимо проверить на соответствие правилам проектирования и произвести экстракцию паразитных параметров с учетом реального размещения элементов и проводников на кристалле. Для решения всего комплекса задач верификации топологии ИС предназначены пакеты Diva, Dracula, Assura. Они содержат средства проверки правил проектирования (DRC), позволяют сравнить разработанную топологию со списком цепей или принципиальной схемой (LVS). С помощью средств верификации из топологии можно экстрагировать паразитные параметры (RCX) и временные задержки, а затем с их учетом промоделировать схему. Проектирование СБИС с использованием современных технологий (0,13 мкм и менее) становится невозможным без детального анализа разработанной топологии, учета влияния на временные характеристики кристалла наводок и помех на проводниках и разброса напряжения питания на ячейках. Diva - набор инструментальных средств проверки, который позволяет находить и исправлять ошибки проекта. Использование обработки слоев для подготовки данных, Diva проверяет физический проект, электрическое функционирование и выполняет сравнение топологии со схемой. Diva помогает найти ошибки в процессе проектирования и позволяет просматривать их в интерактивном режиме, помогая ускорить диагноз ошибок и их исправление. Diva также позволяет выполнять инкрементальные проверки в областях, которые были изменены Приобретаемые компетенции: В результате изучения дисциплины слушатели должны: - знать возможности интегрированной системы моделирования Сadence; отдельные программные средства автоматизированной системы Сadence; маршрут сквозного проектирования цифровых и аналоговых схем. - уметь работать в графическом схемотехническом редакторе Virtuoso; разрабатывать символьные представления для описания функциональных блоков; выполнять моделирование схем из оболочки Analog Affirma Environment; выполнять описание функциональных блоков на Verilog и моделирование на поведенческом уровне; определять параметры, характеризующие работу схем, по полученным зависимостям в окне Vaweform; обрабатывать полученные результаты с помощью программы Calculator. - иметь опыт выполнения сквозного маршрута проектирования интегральной схемы; проектирования цифровых и аналоговых ИС; анализа полученных результатов; составления отчетов о работоспособности разрабатываемого устройства. - иметь представление об особенностях проектирования различных типов схем; о тенденциях и перспективах развития современных методов проектирования средствами САПР. Изучение программы повышения квалификации базируется на следующих областях знаний: твердотельная электроника, информатика, микросхемотехника, стандартные программы проектирования интегральных схем. Для успешного усвоения программы повышения квалификации наиболее важными являются: основные электрические свойства полупроводников (твердотельная электроника); работа в операционной системе WINDOS, Unix (информатика), особенности проектирования цифровых и аналоговых интегральных схем (микросхемотехника), схемотехническое проектирование (стандартные программы проектирования интегральных схем). Навыки и умение, полученные в процессе изучения этой программы повышения квалификации, могут быть использованы при выполнении проектирования цифровых и аналоговых ИС.