1. Введение Этот документ описывает функциональные

реклама

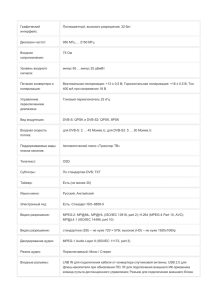

1. Введение Этот документ описывает функциональные возможности и электрические характеристики бесконтактных устройств чтения/записи MFRC523. 2. Общее описание MFRC523 это высоко интегрированный считыватель/записыватель для бесконтактной связи на 13,56 МГц. MFRC523 Считыватель поддерживает ISO / IEC 14443 / MIFARE режиме. внутренний передатчик MFRC523 в состоянии принять привод чтения / записи антенны, направленные на общаться с ISO / IEC 14443 / карт MIFARE и транспондеров без дополнительных Активные схемы. Приемник Модуль обеспечивает надежную и эффективную реализацию демодуляции и декодирования сигналов с ISO / IEC 14443 / MIFARE совместимых карт и транспондеров. Цифровой модуль управляет полным ISO / IEC 14443 и разработки обнаружение ошибок (паритет и КПР) функциональности. MFRC523 поддерживает MIFARE Mini, MIFARE 1K и 4K MIFARE (MIFARE стандарт) продукции. MFRC523 поддерживает бесконтактные связи и использует MIFARE выше скорость передачи данных до 848 kBd в обоих направлениях. MFRC523 поддерживает все слои ISO / IEC 14443 читателя B / писатель связи Протокол предусматривает, что внешние компоненты, такие как генератор, блок питания и катушки, а стандартных протоколов, таких как ISO / IEC 14443-4 и / или ISO / IEC 14443 B являются антиколлизии правильно выполнены. Отметим, что использование этого устройства NXP Semiconductors в соответствии с ISO / IEC 14443 B может ущемлять прав третьих лиц патента. Он несет ответственность за Пользователь меры по обеспечению надлежащего сторонних лицензий патент существует. Следующие интерфейсы хоста условии, что: • Последовательный периферийный интерфейс (SPI) • Серийный UART (по аналогии с RS232 с уровнем напряжения в зависимости от контактный напряжения питания) • I2С-интерфейс шины 3. Особенности и преимущества В "высокой комплексной схемы для демодуляции аналоговых и расшифровать ответы В "Buffered драйверами вывода для подключения антенны с минимальным числом внешних компонентов В "Поддержка ISO / IEC 14443 / MIFARE В "Поддержка ISO / IEC 14443 B чтения / записи режимов В "Типичные рабочее расстояние в чтение / режиме записи до 50 мм в зависимости от Размер антенны и настройка В "Поддержка MIFARE Mini, MIFARE 1K и 4K MIFARE шифрования чтение / режиме записи В "Поддержка ISO / IEC 14443 выше скорость передачи сообщения по 212 kBd, 424 kBd и 848 kBd В "Поддержка MFIN / MFOUT В "Дополнительный встроенный блок питания на смарт-карты IC подключен через MFIN / MFOUT В "Поддерживаемые интерфейсы принимающей В <SPI до 10 Мбит / с В <I 2С-интерфейс шины до 400 kBd В быстром режиме, до 3400 kBd в высокоскоростном режиме В <серийный RS232 UART до 1228,8 kBd с уровнем напряжения в зависимости от контактный напряжение питания В "FIFO буфером 64 байт ручками отправлять и получать В "Гибкие режимы прерываний В "Hard Reset с низким степенной функции В "Power-вниз программного обеспечения режиме В "программируемый таймер В "внутреннего генератора для подключения кварцевого резонатора 27,12 МГц В "2,5 V до 3,3 V питания В "Конвенции о правах ребенка сопроцессор В "Программируемые ввода / вывода В "Внутренняя самодиагностика 4. Краткий справочник данных [1] напряжения питания ниже 3 V снижения производительности, например, достижимых рабочее расстояние. [2] VDDA, VDDD и VDD (TVDD) всегда должно быть то же напряжение. [3] VDD (PVDD) всегда должно быть таким же или меньшим напряжением, чем VDDD. [4] ИПД полного тока для всех поставок. [5] IDD (PVDD) зависит от общей нагрузки на цифровой булавки. [6] IDD (TVDD) зависит от VDD (TVDD) и внешней цепи, связанные с булавками TX1 и TX2. [7] Во время типичная операция по схеме, общий ток не превышает 100 мА. [8] Типичные значения с помощью дополнительных драйверов и конфигурации антенны соответствуют 40 Ω между контактами TX1 и TX2 на 13,56 МГц. 6. Блок-схема Аналоговый интерфейс обрабатывает модуляции и демодуляции аналоговых сигналов. Бесконтактный UART управляет требований протокола для связи протоколов в сотрудничестве с хозяином. Буфер FIFO обеспечивает быстрый и удобный данных трансфер в и из принимающей страны и бесконтактных UART, и наоборот. Различные интерфейсы хоста в целях удовлетворения различных требований заказчика. 7, Информация о выводах 7.1 Описание выводов Таблица 3. Pin описание Pin Символ типа [1] Описание 1I2C II 2С-шины позволяют вход [2] 2 PVDD P поставки контактный 3 DVDD P цифровой блок питания 4 DVSS G цифровой земли [3] 5 PVSS G контактный блок питания земле 6 NRSTPD сбросить и выключения ввода: выключения: включается, когда LOW; внутренних текущих раковины выключены, генератор тормозится и ввода контактов отключается от внешнего мира сброс: включен положительным краем 7 MFIN я MIFARE входного сигнала 8 MFOUT сигнал о выходе MIFARE 9 SVDD P MFIN и MFOUT контактный блок питания 10 TVSS G передатчика выходного каскада 1 землю 11 TX1 O передатчика 1 модулированных 13,56 МГц энергоносителя выходной 12 TVDD P мощность передатчика поставки: поставка выходного каскада передатчика 1 и 2 13 TX2 O 2 передатчика модуляции 13,56 МГц энергоносителя выходной 14 TVSS G передатчика выходного каскада 2 земле 15 AVDD P аналогового питания 8.3.4 I2C Интерфейс шины I2С-шина (Inter-IC) интерфейс поддерживается, чтобы недорогой низких оценок контактного последовательного шина интерфейс к хосту. I2С-интерфейс реализован в соответствии с NXP Semiconductors "I2С спецификации интерфейса, ред. 2,1 января 2000 года. Интерфейс может работать только в режиме Slave. Поэтому MFRC523 не реализует генерации тактирования или доступ арбитраж. Ри с 11. I2C-bus interface M FRC523 может работат ь как в качеств е ведомог о приемни ка так и ведомого передатчика, в стандартном режиме, быстром режим и высоко-скоростном режиме. SDA является двунаправленной линией подключены к положительному выводу напряжения питания с использованием источника тока или нагрузочного резистора. Оба SDA и SCL линии установлены высоко, когда данные не передаются. MFRC523 имеет 3-состояние выходного каскада для выполнения проводных и функции. Данные о I2С-шины могут быть переданы на скоростях до 100 kBd в стандартном режиме, до 400 kBd В быстром режиме и до 3,4 Мбит/с в высокоскоростном режиме. Если I2С интерфейс выбран пик подавления включена линии SCL и SDA как это определено в I2С спецификации интерфейса. См. таблицу 155 на стр. 77, для временных требований.