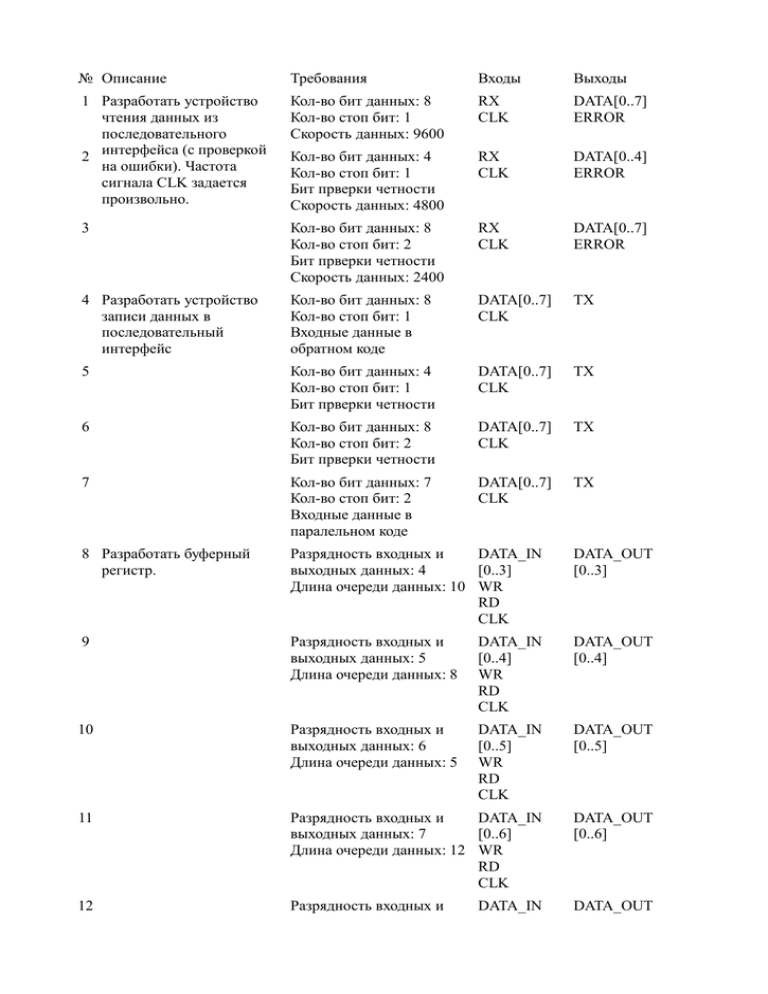

Описание Требования Входы Выходы 1 Разработать устройство

реклама

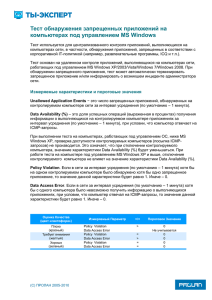

№ Описание Требования Входы Выходы 1 Разработать устройство чтения данных из последовательного 2 интерфейса (с проверкой на ошибки). Частота сигнала CLK задается произвольно. Кол-во бит данных: 8 Кол-во стоп бит: 1 Скорость данных: 9600 RX CLK DATA[0..7] ERROR Кол-во бит данных: 4 Кол-во стоп бит: 1 Бит прверки четности Скорость данных: 4800 RX CLK DATA[0..4] ERROR 3 Кол-во бит данных: 8 Кол-во стоп бит: 2 Бит прверки четности Скорость данных: 2400 RX CLK DATA[0..7] ERROR 4 Разработать устройство записи данных в последовательный интерфейс Кол-во бит данных: 8 Кол-во стоп бит: 1 Входные данные в обратном коде DATA[0..7] CLK TX 5 Кол-во бит данных: 4 Кол-во стоп бит: 1 Бит прверки четности DATA[0..7] CLK TX 6 Кол-во бит данных: 8 Кол-во стоп бит: 2 Бит прверки четности DATA[0..7] CLK TX 7 Кол-во бит данных: 7 Кол-во стоп бит: 2 Входные данные в паралельном коде DATA[0..7] CLK TX 8 Разработать буферный регистр. Разрядность входных и DATA_IN выходных данных: 4 [0..3] Длина очереди данных: 10 WR RD CLK DATA_OUT [0..3] 9 Разрядность входных и выходных данных: 5 Длина очереди данных: 8 DATA_IN [0..4] WR RD CLK DATA_OUT [0..4] 10 Разрядность входных и выходных данных: 6 Длина очереди данных: 5 DATA_IN [0..5] WR RD CLK DATA_OUT [0..5] 11 Разрядность входных и DATA_IN выходных данных: 7 [0..6] Длина очереди данных: 12 WR RD CLK DATA_OUT [0..6] 12 Разрядность входных и DATA_OUT DATA_IN выходных данных: 8 Длина очереди данных: 9 [0..7] WR RD CLK 13 Разработать устройство преобразования информации из восьмеричного в шестнадцатеричный код. 14 Формат входного числа: ххх, где х — одно число в восьмеричном коде (например 101). Результат выдается после приема трех входных чисел 15 Запись входных данных: последовательная. Выдача результата: последовательная DATA_IN[0.. DATA_OUT 2] [0..3] Запись входных данных: последовательная. Выдача результата: параллельная DATA_IN[0.. DATA_OUT 2] [0..х] Запись входных данных: параллельная. Выдача результата: последовательная DATA_IN[0.. DATA_OUT х] [0..3] 16 Запись входных данных: параллельная. Выдача результата: параллельная DATA_IN[0.. DATA_OUT х] [0..х] 17 Запись входных данных: DATA_IN[0.. DATA_OUT1 последовательная. 2] [0..3] Выдача результата: DATA_OUT3 последовательная по трем [0..3] различным линиям DATA_OUT3 [0..3] 18 Разработать арифметическое устройство. Коды операций: «+» - 001, «-» 010, «*» - 011, «mod 2» 19 100. Сигнализировать о наличии переполнения или заема Разрядность чисел: 8 Операции: +,Формат входных данных: двоичный DATA_IN_A [0..7] DATA_IN_B [0..7] DATA_OUT [0..7] P Q Разрядность чисел: 6 Операции: -,mod 2 Формат входных данных: двоичный DATA_IN_A [0..5] DATA_IN_B [0..5] DATA_OUT [0..8] P Q 20 Разрядность чисел: 4 Операции: +,Формат входных данных: шестнадцатеричный DATA_IN_A [0..3] DATA_IN_B [0..3] DATA_OUT [0..4] P Q 21 Разрядность чисел: 8 Операции: * Формат входных данных: DATA_IN_A DATA_OUT [0..7] [0..12] DATA_IN_B P [0..7] двоичный [0..7] Q 22 Разрядность чисел: 4 Операции: * Формат входных данных: шестнадцатеричный DATA_IN_A [0..3] DATA_IN_B [0..3] DATA_OUT [0..7] P Q 23 Разрядность чисел: 8 Операции: +,mod 2 Формат входных данных: двоичный DATA_IN_A [0..7] DATA_IN_B [0..7] DATA_OUT [0..7] P Q 24 Разработать запоминающее устройство с возможностью записи/чтения данных по определенному адресу. При выходе адреса за 25 границу памяти выдавать сигнал ошибки. Запись в ЗУ производится только во время установки сигнала WR. Размер памяти: 64*8 Ввод: последовательный Вывод: параллельный DATA_IN ADDRESS [0..x] WR CS CLK DATA_OUT [0..7] ERROR Размер памяти: 64*8 Ввод: параллельный Вывод: параллельный DATA_IN [0..7] ADDRESS [0..x] WR CS CLK DATA_OUT [0..7] ERROR 26 Размер памяти: 64*8 DATA_IN Ввод: параллельный [0..7] Вывод: последовательный ADDRESS [0..x] WR CS CLK DATA_OUT ERROR 27 Размер памяти: 128*4 Ввод: параллельный Вывод: параллельный DATA_IN [0..3] ADDRESS [0..x] WR CS CLK DATA_OUT [0..3] ERROR 28 Размер памяти: 128*4 DATA_IN Ввод: параллельный [0..3] Вывод: последовательный ADDRESS [0..x] WR CS CLK DATA_OUT ERROR 29 Размер памяти: 128*4 Ввод: последовательный Вывод: параллельный DATA_OUT [0..3] ERROR DATA_IN ADDRESS [0..x] WR CS CLK Размер памяти: 256*2 Ввод: параллельный Вывод: параллельный 30 Распределение вариантов по подгруппам: КС-061(1) IЛЬЗIТ Денис ГРАБ Вiталiй ЖУРКО Олександра ЄВГРАШИН Олександр КАЛЯЗIНА Катерина КРУЧКО Юрiй МIРОШНИЧЕНКО Денис ТРОЦЕНКО Марина ГЕРАСИМЕНКО Антон РЕУЦКИЙ Вячеслав 1 24 15 7 29 6 30 2 11 14 КС-061(2) ЕФИМОВ Александр ИВАНЮК Юрий КИРИЧЕНКО Андрей КОТЕЛЕНЕЦ Александр НЕСТЕРЕНКО Светлана ОМЕЛЬЧУК Сергей ОРИЩЕНКО Виктория СМИРНЯГИНА Юлия ХАЙНИЦКАЯ Анастасия 3 8 16 23 27 19 4 18 5 КС-061(3) ГЛАМАЗДА М ЖЕЛИБА В ЗАВОРОТНИЙ И КАШНИКОВА Ю КАШУК Е КУЗНЕЦОВ А НЕХАЙ В ПАНЬОК И ХАЙРУЛИН М ЧЕБАКОВА Т ЮРЧЕНКО К 22 7 17 6 9 12 26 10 25 13 20 DATA_IN [0..1] ADDRESS [0..x] WR CS CLK DATA_OUT [0..1] ERROR КС-062(1) АБЛАМСЬКИЙ Денис Олегович АВВАКУМОВА Анжела Юрiївна АРЗАМАСЦЕВА Катерина Артурiвна ГРЕБЕННIКОВ Євгенiй Олександрович КИРИЧЕНКО Вiталiй Владиславович КОСТИРКО Владислав Сергiйович КОШОВИЙ Артем Володимирович КУЗЬМЕНКО Артем Вiкторович НIКIТIН Валерiй Олександрович ЧИРВОН Антон Олександрович 21 28 2 10 6 18 3 24 30 9 КС-062(2) ГРИНЬ КОНОВАЛОВ КУБРАК ОСАДЧИЙ ПАЦЮК РЯБЧЕНКО СДИТАНОВ ЧАДЮК ХАРЕВ ШУМСКИЙ 1 5 26 2 17 11 29 3 4 30 СП-061(1) АНДРОСОВИЧ Николай БОГОМОЛЕЦ Сергей БОНДАРЕНКО Игорь БОНДАРЬ Тарас ЗИНЧЕНКО Алексей КАДУШКО Наталья КАЛОША Алексей КИРИЧОК Александр КРИВОПАЛАЯ Анастасия ЛИПОВАТЫЙ Роман ЛЯШЕНКО Богдан МЕЛЬНИЧЕНКО Татьяна МУШКЕТИК Иван 28 17 15 5 14 8 27 30 1 16 29 2 26 СП-061(2) ЕРМОТЕНКО Татьяна КАЛИТА Алексей ПЕТРОВ Евгений РЕЗНИЧЕНКО Светлана СИЗЕНКО Марина ТЕВКУН Мария ХАРЧЕНКО Иван ЧЕХ Артем ЧОРНИЙ Тарас ШАМА Дарина ШУГАЛИЙ Андрей 11 25 8 13 24 9 23 18 17 5 21 Если в по какой либо причине не нашли себя в списке просьба обратиться к преподавателю и уточнить задание.