АРХИТЕКТУРА ПЛИС ТИПА ППВМ С ОДНОУРОВНЕВОЙ

реклама

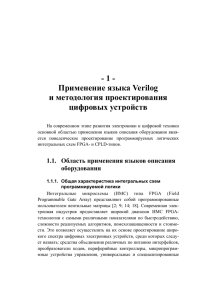

УДК 621.3 АРХИТЕКТУРА ПЛИС ТИПА ППВМ С ОДНОУРОВНЕВОЙ СТРУКТУРОЙ МЕЖСОЕДИНЕНИЙ А.В. Строгонов, С.И. Давыдов, А.В. Арсентьев, М.С. Мотылев, Д.С. Шацких В статье рассматривается архитектура ПЛИС типа ППВМ с одноуровневой структурой межсоединений Ключевые слова: программируемые пользователем вентильные матрицы, логический блок, структура межсоединений Развитие ПЛИС идет по трем направлениям: совершенствование структуры логических блоков (ЛБ); структуры межсоединений (трассировочных ресурсов) и переход на новые технологические поколения, обеспечивающий непрерывный рост числа эквивалентных вентилей на кристалле. Большинство коммерческих архитектур ПЛИС типа ППВМ (программируемые пользователем вентильные матрицы) по технологии статических ОЗУ имеет одноуровневую структуру, когда логические блоки окружены с четырех сторон межсоединениями горизонтальных и вертикальных трассировочных каналов, равномерно распределенных по всей площади кристалла (рис.1) или многоуровневую структуру (рис.2). Рис.1. Одноуровневая структура межсоединений ППВМ Строгонов Андрей Владимирович – ВГТУ, д-р техн. наук, профессор, тел. (473) 243-76-95, e-mail: andreistrogonov@mail.ru Давыдов Сергей Игоревич – ВГТУ, аспирант, тел. (473) 243-76-95, e-mail: sedpo4ta@gmail.com Арсентьев Алексей Владимирович – ВГТУ, ст. преподаватель, тел. (473) 243-76-95, e-mail: sci.aleksei@mail.ru Мотылев Максим Сергеевич – ВГТУ, аспирант, тел. (473) 243-76-95, e-mail: hurricane14@yandex.ru Шацких Дмитрий Сергеевич. – ВГТУ, аспирант, тел. (473) 243-76-95, e-mail: d.shackih@mail.ru 13 Рис.2. Многоуровневая структура межсоединений ПЛИС типа ППВМ (FLEX10K, APEX, APEX II фирмы Altera) В ПЛИС семейств Stratix используется трехсторонняя трассировочная структура, а в ПЛИС Virtex-5 двухсторонняя (рис.3). Уровень 1 использует прямые соединения, а уровень 2 и 3 программируемые соединения, которые отмечены кружками в пересечениях соединений. С повышением уровня соединений, при удалении от логических блоков, возрастает ширина трассировочных каналов. Рис.3. Трассировочная структура межсоединений в ПЛИС Stratix фирмы Altera и Virtex фирмы Xilinx Большинство фирм выпускает сложные одноуровневые ПЛИС, располагая LUT-таблицы входящие в состав ЛБ в виде квадратной матрицы на площади кристалла, при этом связи между LUT- таблицами выполняются в виде соединений (треков или дорожек), разделенных на отдельные участки (сегменты) электронными ключами (рис.4). Рис.4. Архитектура ПЛИС Xilinx 3000 Иерархическая (многоуровневая) организация ПЛИС позволяет улучшить их технические характеристики (рис.2). Логические блоки в этом случае группируются в кластеры (например, в конфигурируемый логический блок ПЛИС семейства FLEX10K фирмы Altera входит 8 логических блоков), имеющие свою собственную локальную шину межсоединений. Логические блоки обмениваются сигналами через шины межсоединений верхнего уровня. Межсоединения непрерывны (т.е. не разделены на сегменты электронными ключами), что обеспечивает малые задержки распространения сигналов между логическими блоками и позволяет существенно сократить количество электронных ключей. В данной статье рассмотрим открытую архитектуру ПЛИС разработанную в университете Торонто (Торонто, Канада). Данная архитектура близка к ранним архитектурам ПЛИС Xilinx серий XC3000 и XC4000 (рис.4), для которой характерно: наличие канальных межсоединений разделенных проходными ключами в коммутационном блоке; прямые межсоединения, соединяющие выходы логического блока (ЛБ) со входами/выходами четырех соседних ЛБ; длинные горизонтальные и вертикальные линии проходящие вдоль всего кристалла; сеть тактовых синхросигналов, охватывающая весь кристалл, подключаемая к синхровходам триггеров ЛБ. ПЛИС представляет массив логических блоков (логических элементов) подключаемых с помощью соединительных блоков C1 и C2 к вертикальным и горизонтальным трассировочным каналам межсоединений (рис.5). Блок С1 подключает один из входов (второй) LUT-таблицы и сигнал set/reset к вертикальному каналу, а блок С2 подключает один из входов (третий) и выход ЛЭ к горизонтальному каналу. Соединительные блоки C1 и C2 представляют собой программируемые коммутаторы на мультиплексорных структурах, позволяющие подключать любое межсоединение из горизонтального или вертикального трассировочных каналов на один из входов логического блока. Блок С2 подключает любое межсоединение из канала ко входу in3, а блок C1 подключает любое межсоединение из канала ко входу in2. В соединительных блоках C1 и C2 в качестве буферных элементов используются два последовательно соединенных инвертора. Коммутация межсоединений в каналалах осуществляется с помощью программируемого коммутатора-маршрутизатора (S-блок). Рис.5. Архитектура ПЛИС типа ППВМ Предлагается использовать эту архитектуру c целью изучения структуры межсоединений и особенности их программирования. Литература 1. www.altera.com. White paper. 40-nm FPGAs: architecture and performance comparison. WP-01088-1.0. December 2008, ver. 1.0. 2. Ian Kuon, Russell Tessier, Jonathan Rose. FPGA Architecture: Survey and Challenges // Foundations and Trends in Electronic Design Automation.Vol. 2, No. 2 (2007) 135–253. 3. Blair Fort, Daniele Paladino, Franjo Plavec. Full Custom Layout of an SRAM-Based FPGA. Final Report. ECE1388. VLSI Desig Methology. Toronto, University of Toronto. December, 2004. 4. Betz V. and Rose J. “How Much Logic Should Go in an FPGA Logic Block?” // IEEE Design and Test Magazine, Spring 1998, pp.10-15. 5. Betz V. and Rose J. “FPGA Routing Architecture: Segmentation and Buffering to Optimize Speed and Density” // IEEE Design and Test Magazine, Spring 1999, pp.23-29. 6. David Lewis et al. “The StratixTM Logic and Routing Architecture”. Proc FPGA-02, pp.12-20. 7. Elias Ahmed and Jonathan Rose. “The Effect of LUT and Cluster Size on Deep-Submicron FPGA Performance and Density”, Proc FPGA-00, pp.3-12. 8. Tomasz S. Czajkowski and Jonathan Rose. A Synthesis Oriented Omniscient Manual Editor FPGA’04, February 22– 24, 2004, Monterey, California, USA, pp.89-98. 9. Ракитин В.В. Интегральные схемы на КМОПтранзисторах М.: 2007, 307 c. Воронежский государственный технический университет ARCHITECTURE FPGA WITH SINGLE-LEVEL STRUCTURE INTERCONNECTION A.V. Strogonov, S.I. Davydov, A.V. Arsentjev, M.S. Motylev, D.S. Shackih In article consider of architecture FPGA with single-level structure interconnection Key words: field-programmable gate arrays, logic blocks, routing architectures