Процесс разработки проекта для ПЛИС в пакете Actel Libero IDE компоненты 68

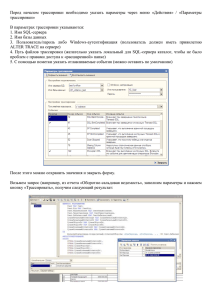

реклама

компоненты 68 Сергей КАРПОВ karpov@actel.ru ПЛИС Процесс разработки проекта для ПЛИС в пакете Actel Libero IDE Размещение и трассировка После того как проект синтезирован и отлажен, необходимо его имплементировать в ПЛИС — произвести размещение и трассировку проекта под конкретную микросхему и сгенерировать файл прошивки. Имплементация производится в пакете Actel Designer, который входит в состав Libero IDE. Сначала произведем конфигурацию. Для этого кликаем по стрелке в верхнем левом углу на кнопке Place&Route и выпадающем меню выбираем Organize Constraint Files. На открывшейся панели добавляем, если не добавлены, файл временных ограничений и файл соответствия цепей номерам выводов. Запускаем Designer, нажав на кнопку Place&Route (рис. 1). При первом запуске откроется панель мастера настройки, в окне которого надо будет выбрать микросхему, корпус, напряжение питания ядра ПЛИС, тип портов ввода/вывода Рис. 2. Окно пакета и панель добавления файлов в проект Рис. 3. Netlist Viewer Рис. 1. Пакет Actel Designer по умолчанию. Если Designer запускается после корректировки проекта, то откроются окно пакета и панель добавления файлов в проект (рис. 2). Проверьте, все ли требуемые файлы присутствуют в списке, и нажмите OK. Сначала необходимо скомпилировать проект, нажав на кнопку Compile. В процессе компиляции производится оптимизация RTL-модели проекта под выбранную ПЛИС с учетом заданных ограничений и назначенных выводов, которые были заданы в соответствующих файлах. Если в процессе анализа не было обнаружено критических ошибок, в окне лога программы по завершении будет сформирован краткий отчет, в котором будет приведена статистика по заполнению микросхемы и по ряду критических цепей. Пакет Designer имеет три группы инструментов для анализа результатов, задания ограничений, размещения и трассировки. Первая группа называется MultiView Navigator, она служит для анализа и задания физических параметров. Вторая, Smart Time, — для анализа и задания временных параметров. Рис. 4. Pin Editor КОМПОНЕНТЫ И ТЕХНОЛОГИИ • № 1 '2009 компоненты ПЛИС Рис. 5. ChipPlanner Третья группа включает в себя лишь один инструмент — Smart Power. Рассмотрим более подробно инструменты каждой группы. Инструменты MultiView Navigator, как правило, используются сравнительно редко. Netlist Viewer позволяет просмотреть результирующую схему после компиляции в виде схемы (рис. 3). Запустив Pin Editor, можно посмотреть физическое распределение цепей по выводам микросхемы и при необходимости его скорректировать (рис. 4). ChipPlanner (рис. 5) позволяет просматривать результаты размещения и трассировки в ПЛИС, а также задавать регионы трассировки, переназначать логические ячейки и цепи. Корректировка трассировки вручную, особенно ПЛИС большого объема, — дело неблагодарное, и на практике практически не применяется. А вот что может представлять интерес для разработчиков, так это задание регионов трассировки. Особенно при работе над проектом команды. Регионы могут быть трех типов. Empty, в котором запрещено размещение любых сигналов и ячеек. Inclusive, в котором обязательно размещаются заданные элементы и сигналы, но могут размещаться и другие. Exclusive, в котором могут размещаться только указанные элементы и сигналы. Для того чтобы задать регион, выберите пункт меню Region и в нем выберите тип требуемого региона (рис. 6). Затем левой клави- Рис. 7. I/O Attribute Editor КОМПОНЕНТЫ И ТЕХНОЛОГИИ • № 1 '2009 69 Рис. 8. Timing Analyzer Рис. 6. Указание региона трассировки шей мышки выделите требуемый регион. Если выбран тип Inclusive или Exclusive, то в меню Region выберите пункт Assign/Unassign, в открывшемся окне выберите требуемые элементы. Последний инструмент этой группы — I/O Attribute Editor (рис. 7) — представляет сводную информацию по выводам микросхемы в виде таблицы и позволяет задавать или корректировать параметры цепей портов ввода/ вывода, такие как номер вывода соответствующего сигнала, стандарт, нагрузочная спо- собность, наличие подтягивающего резистора и т. д. Наибольший интерес для разработчиков представляет оптимизация по быстродействию и потреблению. Поэтому инструменты следующих двух групп рассмотрим подробнее. Timing Analyzer (рис. 8) предоставляет большие возможности по временному анализу цепей. Он выводит информацию о прогнозируемой максимальной частоте после компиляции и результирующей после трассировки по каждой цепи, которые были заданы в качестве тактовых, а также выдает информацию о критических цепях, задержки в которых близки или превышают заданные. Можно проанализировать временные параметры выбранных цепей или типов сигналов, например задержки от выхода регистра до порта или между двумя регистрами. Можно анализировать максимальные или минимальные задержки. С помощью Constraints Editor (рис. 9) можно задавать временные ограничения для трассировки, в том числе графическим способом. Для правильной работы трассировщика в первую очередь необходимо задать значения частот всех тактовых цепей, если они не были заданы в файле ограничений в проекте. Для этого выберите в меню пункт Action и в пункте Constraint — подпункт Clock (рис. 10). В открывшейся панели в окне Clock Source выберите тактовую цепь и введите в соответствующих окнах значе- Рис. 9. Constraints Editor www.kite.ru 70 компоненты ПЛИС Рис. 10. Окно задания параметров тактовых цепей Рис. 13. Панель Smart Power Рис. 11. Окно установки задержки сигнала по входу ния частоты или периода. Можно также изменить скважность сигнала. Нажмите ОК. Повторите вышеописанную процедуру для всех тактовых цепей. Кроме этого, Constraints Editor позволяет задавать большое число ограничений, как для отдельных сигналов, так и для групп. Можно, например, задавать значения минимальной или максимальной задержки по входу (рис. 11) или выходу, задавать минимальные или максимальные задержки для определенных цепей, задавать анализ задержки не каждый такт частоты, а через определенное значение тактов и многое другое. После того как были заданы все необходимые параметры и ограничения, производим размещение и трассировку проекта в ПЛИС. Рис. 12. Панель настройки трассировки Для этого нажмите на кнопку Layout. Откроется панель настройки (рис. 12). На панели можно выбрать оптимизацию по быстродействию или потреблению мощности, отключить или включить размещение и трассировку, выбрать количество проходов трассировки, а также, в случае перетрассировки, использовать предыдущий результат или отменить его. В большинстве случаев подходят настройки, предлагаемые по умолчанию. Нажимаем ОК. После того как трассировка успешно завершена, можно сгенерировать файл прошивки или произвести настройку оптимизации по потреблению. Для оптимизации по потреблению мощности предусмотрен специальный инструмент Smart Power (рис. 13). Оптимизация по потреблению мощности — более сложная процедура, нежели оптимизация по потреблению, и рассказать о ней в рамках данной статьи не представляется возможным. Поэтому ограничимся кратким описанием. Основным принципом оптимизации является анализ потребления отдельных групп потребления микросхемы, таких как статическое и динамическое потребление матрицы ПЛИС, интегрированной памяти, портов ввода/вывода и т. д. не только в активном, но и во всех режимах работы микросхемы (статическом, спящем, сверхмалого потребления Flash*Freeze для ПЛИС IGLOO и ProASIC3L), и составления сценария работы микросхемы во времени. После определения влияющих на потребление элементов и производится настройка оптимизации. В том числе за счет уменьшения быстродействия. Для получения файла прошивки нажмите на кнопку Programming File в окне процесса Designer. На открывшейся панели (рис. 14) Рис. 14. Получение файла прошивки для семейств Flash-ПЛИС можно выбрать, что будет программироваться — матрица ПЛИС, интегрированное Flash-ПЗУ или и то и другое, а также можно выбрать состояние выводов микросхемы в процессе программирования. Программирование Flash-ПЗУ пока не рассматриваем, поэтому оставляем настройки по умолчанию и нажимаем Finish. В открывшемся окне настройки файла программирования нажимаем Generate. После трассировки можно проверить работоспособность прошивки в симуляции. Для этого необходимо выполнить обратную операцию — получение из файла трассировки файл RTL-модели с реальными временными задержками. Нажмите на кнопку BackAnnotate и на открывшейся панели нажмите ОК. После завершения генерации файлов закрываем Designer и возвращаемся в Libero IDE, в окне Project Flow запускаем симуляцию, нажав на кнопку Simulation. Если симуляция завершена успешно, переходим к программированию и отладке на плате. ■ Продолжение следует КОМПОНЕНТЫ И ТЕХНОЛОГИИ • № 1 '2009