ЛАБОРАТОРНАЯ РАБОТА №1 - Кафедра ВТ

advertisement

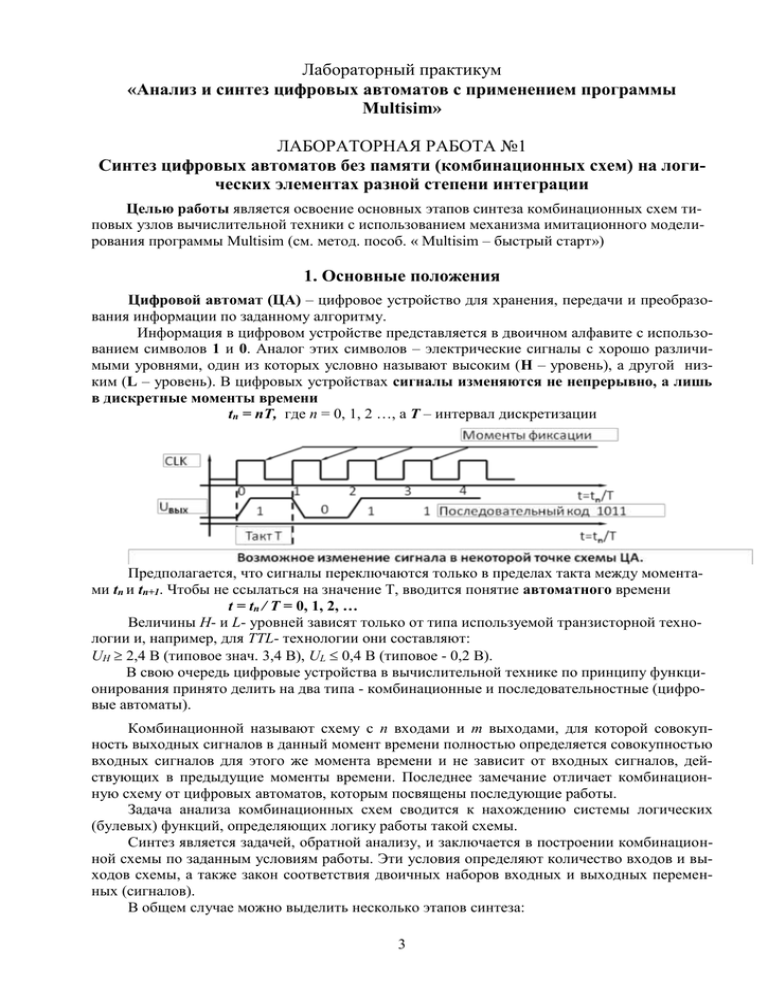

Лабораторный практикум «Анализ и синтез цифровых автоматов с применением программы Multisim» ЛАБОРАТОРНАЯ РАБОТА №1 Синтез цифровых автоматов без памяти (комбинационных схем) на логических элементах разной степени интеграции Целью работы является освоение основных этапов синтеза комбинационных схем типовых узлов вычислительной техники с использованием механизма имитационного моделирования программы Multisim (см. метод. пособ. « Multisim – быстрый старт») 1. Основные положения Цифровой автомат (ЦА) – цифровое устройство для хранения, передачи и преобразования информации по заданному алгоритму. Информация в цифровом устройстве представляется в двоичном алфавите с использованием символов 1 и 0. Аналог этих символов – электрические сигналы с хорошо различимыми уровнями, один из которых условно называют высоким (H – уровень), а другой низким (L – уровень). В цифровых устройствах сигналы изменяются не непрерывно, а лишь в дискретные моменты времени tn = nT, где n = 0, 1, 2 …, а T – интервал дискретизации Предполагается, что сигналы переключаются только в пределах такта между моментами tn и tn+1. Чтобы не ссылаться на значение Т, вводится понятие автоматного времени t = tn / T = 0, 1, 2, … Величины H- и L- уровней зависят только от типа используемой транзисторной технологии и, например, для TTL- технологии они составляют: UH 2,4 В (типовое знач. 3,4 В), UL 0,4 В (типовое - 0,2 В). В свою очередь цифровые устройства в вычислительной технике по принципу функционирования принято делить на два типа - комбинационные и последовательностные (цифровые автоматы). Комбинационной называют схему с n входами и m выходами, для которой совокупность выходных сигналов в данный момент времени полностью определяется совокупностью входных сигналов для этого же момента времени и не зависит от входных сигналов, действующих в предыдущие моменты времени. Последнее замечание отличает комбинационную схему от цифровых автоматов, которым посвящены последующие работы. Задача анализа комбинационных схем сводится к нахождению системы логических (булевых) функций, определяющих логику работы такой схемы. Синтез является задачей, обратной анализу, и заключается в построении комбинационной схемы по заданным условиям работы. Эти условия определяют количество входов и выходов схемы, а также закон соответствия двоичных наборов входных и выходных переменных (сигналов). В общем случае можно выделить несколько этапов синтеза: 3 1. Формирование логических условий работы рассматриваемой схемы или узла путём составления таблицы истинности для каждого из выходов комбинационной схемы. 2. Получение по таблице истинности или на основании использования методов минимизации минимальных нормальных форм в дизъюнктивной или конъюнктивной форме (ДНФ или КНФ). 3. Преобразование минимальных нормальных форм к виду, соответствующему выбранному (или заданному) набору логических элементов (логическому базису). 4. Построение комбинационной схемы. Применительно к данному лабораторному практикуму этот перечень нужно дополнить этапом исследования (моделирования) комбинационной схемы «на рабочем столе» программы Electronics Workbench (последние версии программы ноcят названия Multisim*) на предмет проверки правильности её функционирования. При выполнении практической работы по синтезу комбинационной схемы некоторые этапы могут быть опущены или видоизменены. Так, работа функционального узла может быть задана уже в формализованном виде с помощью системы булевых функций. Не всегда актуальным является и этап минимизации, т.к. комбинационную схему можно реализовать не на основе логических элементов, а используя постоянные запоминающие устройства или программируемые логические матрицы. 2. Индивидуальные задания Индивидуальные задания к работе включают синтез комбинационных схем практически важных функциональных узлов, использующихся в схемотехнике вычислительных устройств. В зависимости от сложности задачи (или её недостаточной освещённости в рекомендуемой литературе) после формулировки задания даются краткие пояснения, следуя которым можно решить поставленную задачу. Выбор логического базиса для реализации схемы осуществляется самостоятельно из состава элементов программы Multisim. Общее замечание к выполнению заданий. Предложенные для синтеза функциональные узлы относятся к комбинационным схемам с несколькими выходами, каждый из которых описывается своей булевой функцией. Поэтому оптимальная схема узла может быть получена лишь при совместной минимизации системы булевых функций (см. соответствующий раздел математической логики), выявляющей общие компоненты (простые импликанты) для различных объединений их этих функций. Задание 1. Пятиразрядный преобразователь прямого кода в дополнительный и обратно (один разряд знаковый, четыре - цифровых). ПОЯСНЕНИЯ к решению [Л.2]. Сопоставление прямого и дополнительного кодов показывает, что последний (для отрицательных чисел) отличается от первого инверсными значениями старших цифровых разрядов после первого справа разряда, содержащего "1". Младший цифровой и знаковый разряд всегда остаётся равными для обоих кодов. Данное правило, применительно к nразрядному коду (ai - разряд числа на входе преобразователя, bi - на выходе), можно записать в следующем виде ((n-1)-й - знаковый разряд): bi = ai (ai-1 V...V a0), i = n-2, n-3, ,1 и bi = ai , для i = 0; n-1. Для положительных чисел: bi = ai, i = n-1, ,0. Схема должна быть единой и выполнять предписанные ей функции независимо от того, какие числа подаются на её вход - положительные или отрицательные в каком-либо из рассматриваемых кодов. С целью упрощения схемы используйте операцию ИСКЛЮЧАЮЩЕЕ ИЛИ (компоненты 74xx86, 74xx386). Задание 2. Приоритетный шифратор PRCD (83) для преобразования 8-разрядного входного кода в двоичный код числа i, где i - номер позиции старшей единицы во входном коде. 4 а0 PRCD а1 А0 а2 А1 а3 А2 а4 а5 cs а6 а7 а) Двоичный код Групповой сигнал а7 а6 а5 а4 а3 а2 а1 а0 GS A2 A1 A0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 0 0 0 0 0 0 0 0 0 1 x 1 0 0 1 0 0 0 0 0 1 x x 1 0 1 0 . . . 0 1 x x x x x x 1 1 1 0 1 x x x x x x x 1 1 1 1 б) Рис. 1.1 Приоритетный шифратор 83(а) и таблица истинности его работы(б) ПОЯСНЕНИЯ к решению [Л.3]. Получение минимальной формы для каждой из функций приоритетного шифратора рис. 1.1 с помощью классических методов минимизации вызывает затруднение, так как число аргументов функции n=8. Однако минимальные формы можно быстро получить, используя два правила из булевой алгебры: правило склеивания xy V x y = x; следствие из дистрибутивного закона x V x y = x V y. Так, например, применяя первое правило к отмеченной строке таблицы истинности для А1, можно получить импликанту a7 a6 a5 a4 a3 a2 , а их совместное использование для двух последних строк позволяет получить а7 V a7 a6 = a7 V a6. Итак, следуя данным рекомендациям, вы быстро определите минимальные формы для каждой из функций. В виду некоторой сложности функций для выходов А2, А1, и А0 построение схемы моделирования в программе EWB-Multisim произвести с использованием подсхем для названных выше функций. Работу схемы сравнить с интегральной схемой SN 74xx148 приоритетного шифратора 8→3 (отечественный аналог 155ИВ1). В библиотеке EWB-Multisim интегральная схема SN 74xx148 с ее входами и выходами выглядит следующим образом: Hазначение входов и выходов: 0…7 – параллельные адресные входы; А0…А2 – выходы, на которых появляется; двоичный код, пропорциональный номеру входа; Е1 – разрешающий вход, который позволяет сделать адресные входы не активными (при Е1=1); Е0 – разрешение по выходу; GS – групповой сигнал; VCC – питание; GND – земля. Рис. 1.2 Приоритетный шифратор 83. В схеме шифратора SN 74xx148 все входы и выход GS по умолчанию считаются инверсными, поэтому таблица состояния шифратора выглядит следующим образом: 5 Е1 1 0 0 0 0 0 0 0 0 0 0 х 1 х х х х х х х 0 1 х 1 х х х х х х 0 1 2 3 х х 1 1 х х х х х х х х х 0 0 1 1 1 1 1 4 х 1 х х х 0 1 1 1 1 5 х 1 х х 0 1 1 1 1 1 6 х 1 х 0 1 1 1 1 1 1 7 х 1 0 1 1 1 1 1 1 1 GS A0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 A1 1 1 0 0 1 1 0 0 1 1 A2 1 1 0 0 0 0 1 1 1 1 Е0 1 0 1 1 1 1 1 1 1 1 Рис. 1.3 Таблица истинности работы шифратора SN 74xx148 Задание 3 включает две части: построение одноразрядного сумматора на сдвоенном мультиплексоре 41 (SN 74xx153 или К155КП2); разработку схемы сопряжения мультиплексоров “8→1” (SN 74xx151 или 155КП7) и “4→1” (SN 74xx153) с целью получения устройства с функциями мультиплексора 161. ПОЯСНЕНИЯ к решению [Л.4]. Изображение сумматора и мультиплексора на функциональной схеме приведено соответственно на рис. 1.4, а и б, где приняты следующие обозначения: ai и bi - одноимённые i - разряды слагаемых, si - разряд суммы, а ci и ci+1 - переносы в i-й и (i+1) - разряды соответственно. ai SM S D si 0 1 2 3 EN bi P ci ci+1 а) Адресные входы A2 A1 x 0 0 1 1 x 0 1 0 1 “Верхняя” половина MS Входы Выход 0 1 2 3 EN F1 x x x x D0 x x x x D1 x x x x D2 x x x x D3 1 0 0 0 0 MUX F1 D 0 1 2 3 EN 0 D0 D1 D2 D3 A2 A1 б) К155КП2 F2 D 0 1 2 3 4 5 6 7 EN MUX F F A3 A2 A1 в) К155КП7 г) Рис. 1.4. Одноразрядный сумматор (а), сдвоенный мультиплексор 41 (б), мультиплексор 81 (в), таблица истинности одной половины сдвоенного мультиплексора КП2 (г). Мультиплексор имеет входы информационные D0...D3 и адресные A2, A1. Двоичный код адреса означает номер того информационного входа, который коммутируется на выход F1 (F2) (см. таблицу истинности рис. 1.4, г). Адресные входы для сдвоенного мультиплексора являются общими для обеих половин схемы. В библиотеке EWB-Multisim данные интегральные схемы (74xx151 и 74xx153) с их входами и выходами выглядят следующим образом: 6 а) б) А x 0 0 0 0 1 1 1 1 В x 0 0 1 1 0 0 1 1 С x 0 1 0 1 0 1 0 1 G 1 0 0 0 0 0 0 0 0 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 W 1 #D0 #D1 #D2 #D3 #D4 #D5 #D6 #D7 Рис. 1.5 Мультиплексор «81» 74xx151 (а) и его таблица истинности (б). ИС SN 74xx151 —это восьмиканальный мультиплексор со стробированием. Он имеет вход разрешения G (активный уровень низкий), комплиментарные выходы Y и W, три адресных входа А, В, С (активный уровень - высокий) и информационные входы D0…D7 (рис. 1.5). Одним из полезных применений мультиплексора является использование его в качестве универсального логического модуля для воспроизведения булевых функций. Как следует из таблицы истинности мультиплексора К155КП2 (рис. 1.4, г), уравнение, описывающее его работу для одного из выходов F1, имеет вид (1.1) F1 E ( A2 A1 D0 A2 A1 D1 A2 A1 D2 A2 A1 D3 ) ИС SN 74xx153 – это двойной четырехвходовый селектор-мультиплексор. Он имеет общие адресные входы А и В, информационные входы 1С0…1С3 и 2С0…2С3, собственный выход разрешения 1G (2G) с активным низким уровнем и прямой выход 1Y (2Y). Поставленная выше задача требует реализации на данном мультиплексоре двух функции от трёх переменных ( si = 1(ai, bi, ci) и ci+1 = 2(ai, bi, ci) ). В общем случае на основе мультиплексора могут быть воспроизведены булевы функции от числа переменных n m, где m Рис. 1.6 Сдвоенный мульти- число адресных входов мультиплексора. Случай n=m плексор 41 считается тривиальным в отличие от n > m, когда требуется предварительное разложение искомой функции в ряд Шеннона по m переменным. Пусть n=m+1=3 (т.е. m=2). Представим произвольную булевую функцию y=f(x3, x2, x1) её разложением по переменным x2 и x1 (т.е. тем переменным, которые задаются на адресные входы): y f ( x 3 , x 2 , x1 ) x 2 x1 f0 ( x 3 ,0,0) x 2 x1 f1 ( x 3 ,0,1) x 2 x1 f2 ( x 3 ,1,0) x 2 x1 f3 ( x 3 ,11 , ). (1.2) Здесь f0, f1, f2, f3 – остаточные функции от одного аргумента - переменной x3. Сравнение уравнений (1.1) и (1.2), позволяет выработать подход к реализации метода. В заключение отметим, что функцию si требуется получить на выходе F1 мультиплексора, а функцию ci+1 - на выходе F2. При затруднении с решением, как первой, так и второй частей Задания 3, обратитесь к литературе [Л. 2, 3, 4]. 7 Задание 4 включает две части: построение одноразрядного вычитателя на сдвоенном мультиплексоре 41 (74153 или К155КП2) (описание его работы см. в Задании 3); разработку схемы сопряжения двух дешифраторов DC 38 (SN 74xx138 или К531ИД7) с целью получения устройства с функциями дешифратора 416. ПОЯСНЕНИЯ к решению [Л. 2, 3, 4]. На рис. 1.7, а приведено условное изображение вычитателя и стандартное функциональное обозначение дешифратора DC 38 (К531ИД7, рис. 1.7, б). Для вычитателя приняты следующие обозначения входов и выходов: ai и di - одноимённые разряды операндов вычитателя, si - разряд разности, bi - заём из i-го разряда, а bi+1 - заём из i+1 разряда. ai di x1 x2 x3 si Выч ит а т е ль 1 2 4 b i+1 bi DC &E RD1 RD2 RD3 а) б) 0 1 2 3 4 5 6 7 y0 y1 y7 К531ИД7 Рис. 1.7 Вычитатель (а) и дешифратор К531ИД7 (б) Дешифратор относится к схемам, преобразующим двоичный код на его входах в активный сигнал на одном из его выходов. Полный дешифратор на n-входов имеет 2n выходов. Поэтому при определении дешифратора допустимо сокращённое обозначение его типа DC 3-8 - дешифратор стремя входами и восьмью выходами. Дешифратор К531ИД7 имеет инверсные выходы (активный низкий уровень), что и отражено на функциональном обозначении. Для решения вопросов Задания 4 рекомендуется использование методики, принципиальные положения которой изложены к Заданию 3. В библиотеке EWB- Multisim интегральная схема SN 74xx138 с ее входами и выходами выглядит следующим образом: а) б) G2A 0 x x G2B x 1 x G1 x x 0 A x x x B x x x C x x x Y0 1 1 1 Y1 1 1 1 Y2 1 1 1 Y3 1 1 1 Y4 1 1 1 Y5 1 1 1 Y6 1 1 1 Y7 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 Рис. 1.8 Дешифратор 74xx138 (а) и его таблица истинности (б) 8 Задание 5. Синтез 4-разрядной схемы инкрементора/декрементора, условное изображение которой, с учётом назначений входов и выходов, приведено на рис.1.9. Для упрощения схемы используйте операцию ИСКЛЮЧАЮЩЕЕ ИЛИ (компоненты 74xx86, 74xx386). ПОЯСНЕНИЕ к решению [Л.3] Таблица 1.1 Из функционального назначения схемы слеY ai qi si qi+1 Режим дует, что при Y=0 между значением разряда ai 0 0 0 0 0 входного слова А и переносом в этот разряд qi=ci 0 0 1 1 0 должна выполняться операция сложения, а при 0 1 0 1 0 Инкремент 0 1 1 0 1 Y=1 между разрядом ai и заёмом qi=bi – вычита1 0 0 0 0 ния. Структура таблицы истинности приведена в 1 0 1 1 1 Декремент таблице 1.1. 1 1 0 1 0 Определив значения для функций выходов si 1 1 1 0 0 и qi+1, можно получить необходимые логические соотношения, которые будут справедливыми для i=1, 2, 3. В дальнейшем надо только определиться с начальными значениями переноса/заёма при формировании функций so и q1 (i=0). Задание 6. Преобразователь 4-разрядного двоичного кода в код Грея и обратно. Логический базис – элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (компоненты 74xx86, 74xx386). 4 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 ПОЯСНЕНИЯ к решению [Л. 2 ,3 ,4]. В некоторых случаях необходим числовой код, построенный таким образом, чтобы при переходе от одного числа к следующему Таблица 1.2 изменялся бы всегда только один двоичный разряд. Двоичный код Код Грея Этим свойством обладает код Грея, 3 2 1 4 3 2 1 использующийся, например, при разметке 0 0 0 0 0 0 0 координат клеток карт Карно, в преобразо0 0 1 0 0 0 1 вателях углового положения вала в цифро0 1 0 0 0 1 1 вой код и в других случаях. Соответствие 0 1 1 0 0 1 0 между двоичным кодом и кода Грея для че1 0 0 0 1 1 0 тырехразрядных чисел отражено в табл. 1.2. 1 0 1 0 1 1 1 Используя стандартную методику син1 1 0 0 1 0 1 теза с минимизацией на картах Карно, мож1 1 1 0 1 0 0 но легко решить прямую задачу. Решение 0 0 0 1 1 0 0 обратной задачи (преобразования кода Грея 0 0 1 1 1 0 1 в двоичный код) – сложнее. Сложность за0 1 0 1 1 1 1 ключается в преобразовании минимальных 0 1 1 1 1 1 0 логических форм типа И/ИЛИ к виду, ис1 0 0 1 0 1 0 1 0 1 1 0 1 1 пользующему только операцию 1 1 0 1 0 0 1 ИСКЛЮЧАЮЩЕЕ ИЛИ (mod 2). Решение 1 1 1 1 0 0 0 можно значительно упростить, если рас9 смотреть карты Карно для функций выходов i (i= 1, 2, 3, 4) как объекты преобразования одной функции в другую на основе операции ИСКЛЮЧАЮЩЕЕ ИЛИ. Для пояснения высказанного предложения на рис.1.10 приведены карты Карно для функций выходов 3 и 2. Сравнение этих карт Карно между собой позволяет убедиться в преобразовании карты Карно для 3 в карту для 2 на основе соотношения: 2 = 3 2 = 3 2 V 3 2. 2 1 4 3 00 01 11 10 а) 3 00 01 11 10 1 1 1 1 1 1 1 2 1 4 3 00 01 11 10 1 б) 2 00 01 1 1 1 11 1 10 1 1 1 1 Рис. 1.10 Карты Карно для переменных 3 и 2 Если это понятно, то решение обратной задачи не вызывает затруднений. Задание 7. Исследование работы многоразрядного сумматора с последовательным переносами ПОЯСНЕНИЯ к решению [Л.3, 4, 8]. Исследование работы многоразрядного сумматора провести в три этапа. Построить схему одноразрядного сумматора и оформить её как подсхему (Subcircuit); Построить 4- разрядный сумматор с последовательным переносом на основе одноразрядного сумматора; Произвести исследование схемы 4-разрядного арифметико-логического устройства (АЛУ) К155ИП3 (SN 74xx181) в режиме суммирования. Представление этой схемы в EWB-Multisim показано на рис.1.11 , а описание его работы при активных низких и высоких уровнях отображено на рис.1.12 и рис.1.13 соответственно. АЛУ SN 74xx181 может выполнять 16 логических или 16 арифметических операций. Он имеет входы А0…А3 и В0…В3, на которые можно подать два четырехразрядных слова А и В. Входы S0…S3 позволяют выбрать 16 функций устройства, однако благодаря входу М число функций можно увеличить в два раза. Вход СN принимает входной сигнал переноса. Результат виден на выходах F0…F3. G –выход генерации переноса, Р – выход распространения переноса, А=В- выход компаратора (выход с открытым коллектором, подключается к источнику питания через резистор 1 кОм). Рис. 1.11 4-разрядный двоичное АЛУ с ускоренным переносом SN 74xx181 В силу самодвойственности выполняемых операций таблица выполняемых операций приводится в двух вариантах. При этом следует иметь ввиду, что оба сигнала переноса CN и CO – инверсны относительно сигналов на входах А и В, т.е. когда слова А и В – в положительной логике, сигналу переноса отвечает низкий уровень напряжения, а в отрицательной - наоборот. Логические операции выполняются поразрядно (М=H, внутренние переносы запрещены), арифметические (M=L) – с учётом всех видов переносов (значение «–1» при этом представляется дополнительным кодом в виде набора «1111»). Для организации действий над словами большей разрядности АЛУ используются выходы CN и CO (схема с последовательными переносами между 4- разрядными секциями) или вы10 ходы P и G для получения схемы с параллельными переносами. В последнем случае используется специальная схема формирования ускоренных переносов ИС 155ИП4 (SN 74xx182). Выбор функции S3 S2 S1 S0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Входные данные при активных низких уровнях Логические функции Арифметико-логические операции (на входе М- напр. вы- (на входе М-напряжение низкого уровня) сокого уровня) CN=L (без переноса) CN=H (с переносом) #A #A#B #AB 1 #(AB) #B #(AB) A#B #AB AB B A B 0 A#B AB A A-1 AB-1 A#B-1 -1 A+(A#B) AB+(A#B) A-B-1 A#B A+(AB) A+B A#B+(AB) AB A+A AB+A A#B+A A A AB A#B 0 A+(A#B)+1 AB+(A#B)+1 A-B (A#B)+1 A+(AB)+1 A+B+1 A#B+(AB)+1 (AB)+1 (A+A)+1 AB+A+1 A#B+A+1 A+1 Рис. 1.12 Выбор функции при низких активных уровнях операндов в SN 74181. 11 Выбор функции S3 S2 S1 S0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Входные данные при активных высоких уровнях Логические функции Арифметико-логические операции (на входе М- напр. (на входе М-напряжение низкого уровня) высокого уровня) #CN=H #CN=L (без переноса) (с переносом) #A A A+1 #(AB) AB (AB)+1 #AB A#B (A#B)+1 0 -1 0 #(AB) A+A#B A+A#B+1 #B A#B+(AB) A#B+(AB)+1 AB A-B-1 A-B A#B A#B-1 A#B A+AB A+AB+1 #AB A+B A+B+1 #(AB) B (A#B)+AB (A#B)+AB+1 AB AB-1 AB 1 A+A A+A+1 A#B (AB)+A (AB)+A+1 AB (A#B)+A (A#B)+A+1 A A-1 A Рис. 1.13 Выбор функции при высоких активных уровнях операндов в ИС SN 74xx181. Режим компаратора обеспечивается при M=L и S3 S2 S1 S0=0110. Когда А=В, на выходе «А=В» формируется сигнал высокого уровня (! - выход с открытым коллектором). При этом выходной сигнал переноса CО характеризует соотношение между числами А и В в случае их неравенства согласно нижеследующей таблице. Логическое соглашение Входной перенос CN Соотношение между числами АиВ Выходной перенос CO Положительная логика H L H L L H L H A B A<B A>B AB AB A<B A>B AB H H L L L L H H Отрицательная логика Задание 8. Исследование работы многоразрядного сумматора с параллельными переносами ПОЯСНЕНИЯ к решению [Л.3, 4, 8]. Исследование работы многоразрядного сумматора провести в три этапа. Построить схему одноразрядного сумматора, отвечающего требованиям интерфейса схемы ускоренного переноса (СУП), оформить её как подсхему (схему одноразрядного сумматора согласовать с преподавателем); На основе выведенных соотношений для межразрядных переносов разработать схему ускоренного переноса СУП и оформить её как подсхему (реальный компонент 74xx182, виртуальный La_Carry_Gen из группы Place Misc Digital); Построить 4- разрядный сумматор с параллельным переносом (реальный компонент 74xx83 или 74xx283); 12 11 12 15 14 2 3 6 5 7 A4 B4 A3 B3 A2 B2 A1 B1 CI CO Задание 9. 4-разрядный цифровой ком- 9 паратор, определяющий отношения «равно» и «больше» для двоичных чисел А и В. S4 10 ПОЯСНЕНИЯ к решению. Предлагается на выбор два способа. S3 13 Анализ на истинность указанных соотношений на основе выполнения поразS2 1 рядных логических операций над одноимёнными разрядами обоих чисел. Данный S1 4 способ подробно изложен в [Л. 2, 8] (реальный компонент SN 74xx85). Рис. 1.14. 4-разрядный двоичный сумматор с Выполнение операции вычитания ускоренным переносом К555ИМ6 (SN 74283) А-В на многоразрядном сумматоре (например, ИС К155ИМ6 (SN 74xx283)), с последующим анализом результата вычитания (флагов). Для этого достаточно проанализировать результат выполнения ассемблерной команды Cmp dst, src для беззнаковых операндов. Можно также обратиться и к литературе [Л. 3]. Вместо схемы 4-разрядногосумматора можно использовать схему 4-разрядного АЛУ К155ИП3 (74xx181) в режиме сумматора. Подробное описание его работы см. в Задании 7. Задание 10. Схема вычитания двух 4-разрядных двоичных чисел с вычислением абсолютной величины и знака разности, использующей циклический перенос. ПОЯСНЕНИЯ к решению. Предварительно рассмотрим реализацию операции вычитания двоичных чисел А и В, заменив её сложением числа А с поразрядным дополнением числа В. Поразрядное дополнение числа В вводится соотношением 2n-1-B и, фактически, сводится к простому инвертированию всех разрядов числа A-B = A+2n-1-B = 2n+(A-B)-1. (1.3) В зависимости от знака разности возможны два случая. 1. А-В>0. В этом случае реализация соотношения (1.3) приводит к формированию переноса из старшего разряда CF=2n и для получения правильного результата необходимо выполнить операцию циклического сложения с образовавшимся переносом. 2n+(A-B)-1 + └───> 20 ─────── A-B>0 или |А-В| Отметим, что здесь знак разности можно получить как αs= cf Пример. А=5=0101(2) А = 0101(2) n B=3=0011(2) 2 -1-B = 1100(2) ───────── 1 0001(2) └─> 1 Сложение с циклическим переносом ───── 0010(2)=2 Графическая иллюстрация рассмотренного случая приведена на рис. 1.15. 13 Циклический перенос 2n-1-B A 2n 2n-1 cf Сумматор 20 1 αs=0 A-B>0 или │A-B│ Рис. 1.15. Схема вычитания на основе сложения (A-B>0) А-В≤0. В этом случае перенос при реализации выражения (1.3) не возникает (убедитесь в этом самостоятельно), а вычитание равных чисел приводит к формированию числа 11...1. Модифицируем данный случай для удовлетворения требования, сформулированного в задании – получения модуля разности с указанием её знака. Для этого схемным путём сформируем искусственный перенос (рис 1.16), который бы инициировал операцию поразрядного дополнения величины (1.3) и указывал на наличие отрицательной разности 2n-1-(2n+(A-B)-1) = (B-А) = │A-B│. (1.4) Для выполнения задания нужно объединить схемы рис. 1.15 и 1.16 в одну 2n-1-B A 2n-1 сf=0 Сумматор 20 1 αs αi, i = 0,...,n-1. αs=1 A-B Рис. 1.16. Схема вычитания на основе сложения (A-B≤0) В разрабатываемой схеме можно использовать 4-разрядный сумматор SN 74xx83 (283). Задание 11. Устройство контроля чётности при передаче данных. ПОЯСНЕНИЯ к решению. Простейший способ обнаружения ошибок при передаче данных заключается в передаче разряда проверки на чётность P. (рис. 1.17). В контрольный разряд (КР) чётности записывается «0», если число единиц 8 8 D 8 8 D Канал связи 8 P M2 8 M2 Контрольный разряд чётности P «0» при правильной передаче Рис. 1.17. Передача данных при проверке на чётность в информационном слове чётное и наоборот - в случае нечётного числа. При этом общее количество передаваемых единиц по каналу связи, включая КР, всегда будет чётным. На принимающей стороне КР вычисляется тем же способом для информационных разрядов и сравнивается с переданным КР. При несовпадении фиксируется ошибка передачи. Исправить 14 ошибку, к сожалению, невозможно, - надо использовать более сложные способы помехоустойчивого кодирования данных. При выполнении задания произведите синтез блока формирования КР, а также покажите возможность использования в схеме ИС 1533ИП5 (SN 74xx280). В библиотеке EWB –Multisim интегральная схема SN 74xx280 с ее входами и выходами и таблицей описания работы выглядит следующим образом: а) б) Входы Выходы Число высоких уровней на входах Четное Нечетное EVEN 1 0 ODD 0 1 Схема SN 74xx280 –это девятиразрядная схема контроля четности суммы единиц входного слова. Она имеет девять входов А…I, а также два выхода EVEN (контроль четности) и ODD (контроль нечетности), NC – вывод отключен Рис. 1.18 ИС контроля четности суммы(a) и таблица её состояния (б). Задание 12. Спроектировать сигнальное устройство, зажигающее светодиод, если сработали любые 5 из 7 датчиков. Датчик рассматривать как двухпозиционный электронный ключ (Switch),способный формировать двоичные сигналы «0» и «1». Основным элементом для построения схемы считать одноразрядный сумматор SM. Задание 13. Преобразователь кода 8-4-2-1 в 7-разрядный код семисегментного индикатора для представления 16-теричных чисел: 0, ..., 9, А, b, C, d, E, F. ПОЯСНЕНИЯ к решению. Для вывода чисел широко применяются семисегментные индикаторы, в которых семь сегментов-диодов расположены так, что при зажигании определённой их комбинации высвечивается тот или иной символ (рис. 1.19, а). Выпускаются семисегментные индикаторы с общим анодом или катодом. Для управления сегментами удобны элементы с выходом типа «общий коллектор», так как в этом случае подключается внешний резистор, сопротивление которого можно задать с учётом характеристик применяемых светодиодов (рис. 1.19, б – сегмент зажигается, когда выходной транзистор управляющего элемента отпирается; рис. 1.19, в – отпирается). Vcc Vcc R 0 5 6 D 1 *◊ R 4 а 2 D *◊ 3 б в Рис. 1.19 Семисегментный индикатор (а) и схемы управления сегментом с общим анодом (б) и общим катодом (в) Преобразователь кода 8-4-2-1 в 7-разрядный код семисегментного индикатора для представления 16-теричных чисел 0, ..., 9, А, b, C, d, E, F должен работать в соответствии с таблицей истинности табл. 1.3. В виду некоторой сложности функций для выходов семисег15 ментного дешифратора построение схемы моделирования в программе EWB-Multisim произвести с использованием подсхем для каждой из функций выхода. Проверку работы дешифратора произвести путём подключения к его выходам семисегментного индикатора из библиотеки Multisim10.1. Разрабатываемая схема соответствует виртуальному компоненту в Multisim – BCD_7SEG_DCD – из группы Misc Digital, (реальный компонент - 74xx247(248)). Таблица 1.3 16-теричная цифра 0 1 2 3 4 5 6 7 8 9 A b С D E F Код 7-сегментный выход 8-4-2-1 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 7654-3210 0011-1111 0000-0110 0101-1011 0100-1111 0110-0110 0110–1101 0111–1101 0000–0111 0111–1111 0110–1111 0111–0111 0111–1100 0011–1001 0101–1110 0111–1001 0111–0001 3. Замечания к выполнению работы и содержание отчёта Прежде чем приступить к реализации задания по макетированию и исследованию комбинационной схемы на экране персонального компьютера с помощью программы Multisim, целесообразно выполнить ряд действий ознакомительного характера. 1. Ознакомится с вводным описанием пользователя программы Multisim 10.1. 2. Задание входных сигналов осуществлять с помощью генератора слова (Word Generator) или используя комбинацию из двухполюсных ключей (рис 1.20) 3. Регистрацию выходных сигналов комбинационных схем производить путём их индикации с помощью логических пробников или семисегментных индикаторов. 4. Выполнить необходимые этапы синтеза комбинационной схемы индивидуального задания, учитывая заданный логический базис. Если базис не задан, то проектант свободен в выборе элементов библиотеки элементов EWB-Multisim. Содержание отчёта должно включать Материал последнего пункта данного параграфа, Файл(ы) моделирования разработанной схемы с необходимыми распечатками графических материалов. Рис 1.20. Схема задания Работа подготовил доцент кафедры ВТ НГТУ входных сигналов. В. А. Афанасьев. Редакция 2011 г. 16